#### IConnect007 Presents

16

Final Surface Finish: How Do You Choose?

Study of Immersion Gold Processes Used for Both ENIG and ENEPIG

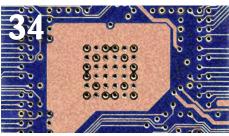

Acid Copper Plating— 34 Understanding What's Often Taken for Granted

**Much More!**

WHAT'SNEWINNEWINPLATINGANDSURFACEFINISHES?

# THE PCB List works

"When I joined Cirexx last year I shared with my colleagues the positive experiences I've had with The PCB List.

We listed Cirexx with a detailed Showcase on The PCB List and it has resulted in quotes and orders!

The PCB List is not only brand and image must for all PCB manufacturers, but also another set of boots on the ground directly generating business."

- Al Wasserzug Sr. Business Development Manager at Cirexx International

# ...and it can work for you!

Over 3000 members are already registered and using THE PCB List.

Get Found! Upgrade to a Showcase and Start Quoting Today.

The best way to find a PCB fabricator, anywhere.

www.thepcblist.com

# Get the spark you need to tune up your sales team.

When an engine doesn't fire on all cylinders, performance is limited. The same goes for your sales team. We provide the spark to get your sales to the next level ...and beyond.

> We've helped dozens of companies big and small improve their bottom line.

Learn how we can help YOU

# January 2017

## Featured Content

# **Plating and Surface Finishes**

So what is new in plating and surface finishes? This month, our experts weigh in on new processes, the tried-and-true old processes, R&D, and how to go about choosing the right process from among all those available today.

### FEATURES:

- **16 Study of Immersion Gold Processes Used for Both ENIG and ENEPIG** *by Don Gudeczauskas, Albin Gruenwald and George Milad*

- 34 Acid Copper Plating–Understanding What's Often Taken for Granted by Michael Carano

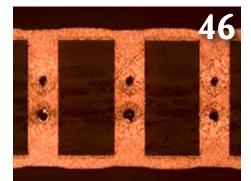

- 46 Electroplated Copper Filling of Through-holes: Influence on Hole Geometry by Ron Blake, Andy Oh, Carmichael Gugliotti, Bill DeCesare, Don DeSalvo, and Rich Bellemare

#### FEATURE COLUMNS:

- **12** Final Surface Finish: How Do You Choose? by Tara Dunn

- 28 Plating and Surface Finish: The Challenges to Electrical Test by Todd Kolmodin

- 60 ENIPIG-Next Generation of PCB Surface Finish MACFEST Dissemination Webinar, December 2016 by Pete Starkey

Limata's Direct Imaging platform sets a new standard for Precision, Performance and Size!

- Precision & small footprint

- Starting under 100K

- R&D labs, university and specific imaging requirements

- Next Gen production class LDI

- Double drawers provide 120+ images/hour

- Soldermask accuracy assured with 64 regional alignment points

- Entry and mid-level production

- 25 micron imaging capabilities

- Precision, Performance and Price!

- 48" x 96" (4' x 8' FEET) image area

- 50 micron imaging capabilities

- Photoresist, soldermask and daylight film ready

Multiple platforms and interchangeable assemblies deliver Precision, Performance and Price without compromise.

**PO** Come see us in booth #3609 and see why we say "We Guide the Light!"

**M-Tech**

USA, Canada +916 473 2140 lino@mtechsales.net

January 2017 Vol. 7, No. 1 thepcbmagazine.com

## HIGHLIGHTS

- 26 Supply Lines

- 44 EIN & Market News

- 64 MilAero007

- 78 Top Ten PCB007

#### DEPARTMENTS

- 80 Events Calendar

- 81 Advertisers Index & Masthead

# **More Content**

#### COLUMNS

- 8 **Everything Old is New Again** *by Patty Goldman*

- 66 Implications of the Trump Presidency by John Mitchell

- 70 Now is the Time for Comprehensive Tax Reform by John Hasselmann

- 74 Fake News: It Could Happen to You by Barry Lee Cohen

#### SHORTS

- 15 Honey, I Shrunk the Circuit

- 32 ETRI Develops High-Performance, Autonomous Vehicle Processor

- 58 An Interview with TTM President Thomas Edman

- 68 Design Your Own Custom Drone

# **185HR** High-Tg, Low-CTE Materials with High Thermal Reliability

### FEATURES

- High Thermal Performance

- Tg: 180°C (DSC) (Base Laminate)

- ▶ Td: 340°C (TGA @ 5% wt loss)

- Low CTE for reliability

- T260: 60 minutes

- T288: >15 minutes

- Lead-free Compatible and RoHS Compliant

- UV Blocking and AOI Fluorescence

High throughput and accuracy during PCB fabrication and assembly

- Superior Processing

Closest to conventional FR-4 processing

- Industry Approvals

- IPC-4101D-WAM1 /98 /99 / 101 /126

- UL File Number E41625

- Qualified to UL's MCIL Program

## **KEY APPLICATIONS**

- Heavy copper, 6 & 12 oz automotive applications

- Military

- Medical

- Industrial

#### Core Material Standard Availability

- Thickness: 0.002" (0.05 mm) to 0.060"/0.062" (1.5 mm)

- Àvailable in full size sheet or panel form

- Prepreg Standard Availability

- Roll or panel form

- Tooling of prepreg panels available

- Copper Foil Type Availability

- Standard HTE Grade 3

- RTF (Reverse Treat Foil)

- Copper Weights

- ½, 1 and 2 oz (18, 35 and 70 μm) available

- Heavier copper available upon request

- Thinner copper foil available upon request

#### Glass Fabric Availability

- Standard E-glass

- Square weave glass fabric available

#### **ORDERING INFORMATION:**

Contact your local sales representative or visit www.isola-group.com for further information.

Isola Group 3100 West Ray Road Suite 301 Chandler, AZ 85226 Phone: 480-893-6527 info@isola-group.com

Isola Asia Pacific (Hong Kong) Ltd.Isola GmbHUnit 3512 - 3522, 35/FIsola StrassNo. 1 Hung To Road, Kwun Tong,<br/>Kowloon, Hong KongD-52348 Dü<br/>Phone: 49-2Phone: 852-2418-1318info-dur@isinfo.hkg@isola-group.comIsola Strass

Isola GmbH Isola Strasse 2 D-52348 Düren, Germany Phone: 49-2421-8080 info-dur@isola-group.com

# **Everything Old is New Again**

by Patty Goldman I-CONNECT007

Happy New Year to all of you faithful and new readers out there! I hope you are looking forward to 2017 as much as we are here at I-Connect007. We have exciting plans for this year and can't wait to get started, but first we need to talk about this month's topic.

This month's issue is all about plating and surface finishes; long ago, that was pretty much my start in the world of printed circuits—wet processing. So this is kind of my home turf and not, since I haven't worked in wet processing for some...well, for many years. I've always expected that I could hop right back onto the plating room floor and pick right up where I left off all those years ago. Or could I? Have things changed much? Time to read on and see.

So what is new in plating and surface finishes? Well it's true that there are still the basic processes—cleaners and microetches, copper and nickel and gold electroplating, immersion tin, nickel, silver—all of which have been around for quite a long time. But with the finer features, the far greater reliability concerns, the lead-free solders, the constant need for lower cost and greater efficiency, etc., the spotlight is often on these "old" processes. Plus, there are a few new ones like ENIPIG.

Much research and development has gone into refining additives for electroplating and electroless/immersion baths to improve the plating quality in one way or another, both on surfaces and in through-holes and vias. Following on that is a tremendous amount of testing to prove out said processes and the subsequent assembly-ability of components. In the end, it's all about reliability, reliability, and reliability.

There are a plethora of final finishes to choose from today. How does one decide? Well, that takes us right to the line-up for this month. Regular columnist Tara Dunn of Omni PCB has

# Unrivaled Speed with Full Automation

ata

## Introducing the atg A8-16a with 16 test probes at an unrivaled test speed of up to 250 measurements per second and full "lights out" Automation.

## Get more info

atg Luther & Maelzer GmbH Zum Schlag 3 • 97877 Wertheim • Germany Phone +49-9342-291-0 • Fax +49-9342-395 10 sales@atg-Im.com • www.atg-Im.com

| Test area:                  | 610 mm x 62  |

|-----------------------------|--------------|

| Number of test heads:       | 16 ( 8 top + |

| Smallest pad / pitch :      | 35 µm (1.4 n |

| Test voltage:               | Up to 1000V  |

| Max. measurements / minute: | Up to 15000  |

| Loading capacity:           | 390 mm , ma  |

| Max board weight:           | 20 lbs       |

| Marking option:             | Barcode labe |

|                             |              |

| 610 mm x 620 mm (24.0" x 24.4")  |

|----------------------------------|

| 16 ( 8 top + 8 bottom side)      |

| 35 µm (1.4 mil) / 80 µm (3.2mil) |

| Up to 1000V                      |

| Up to 15000 measurements /min. * |

| 390 mm , max. 80 kg weight       |

| 20 lbs                           |

| Barcode label                    |

chosen that very subject so it seems appropriate to start with her column on how to choose a final surface finish.

Following this is a study of immersion gold processes—some of that R&D work I mentioned earlier. Don Gudeczauskas, et al, of Uyemura International, present a fine research paper on a comparative study of three immersion gold processes, looking at both solderability and wire bondability.

Lest anyone think that wet processes have no effect on electrical test, Gardien Services' Todd Kolmodin is here to set the record straight with a look at the challenges that plating and surface finishes present to electrical test.

RBP Chemical Technology's Michael Carano is Mr. Plating himself, and he gives us a detailed look at some of those things you might tend to overlook or perhaps take for granted in your acid copper plating process. Rather than talk about controlling the typical constituents, Mike looks beyond at tank parameters and the surrounding process steps.

We are fortunate to have another R&D article, this one by Ron Blake, et al, of MacDermid Enthone Electronics Solutions. They get into another relatively new area for copper electroplating, the filling of through-holes with copper.

Next, our own Pete Starkey reports on a MACFEST development project on a "univer-

sal surface finish," namely ENIPIG (electroless nickel/immersion palladium/immersion gold). This detailed report—including ample test data—has also been recorded as a webinar and can be viewed by clicking on the link near the end of the article.

In keeping with our policy of having a few general interest items for those chemistryphobes out there, we have no less than three columnists weighing in on the U.S. presidential election—in vastly different ways. IPC President John Mitchell starts with a discussion on how the Trump presidency and potential policy shifts may affect the electronics industry. He is followed by guest columnist John Hasselmann, IPC's VP of Government Relations, with a discussion on corporate tax policy and possible changes that may come about with the new administration in Washington, DC.

Regular columnist Barry Lee Cohen compares the "fake news" from this past presidential campaign to the potentially false news that can and probably does occur within and about your own company. Barry also provides some concrete advice on how to keep the communication lines open so news and other information can be quickly disseminated—and any false "news" can be immediately combatted.

IPC APEX EXPO 2017 happens next month (see our calendar of events) and what better time to have our magazine focus on new technology—our topic for February. We expect there to be plenty for you to read about. You can <u>subscribe now</u> and have *The PCB Magazine* delivered to your inbox every month, giving you a head start on all things PCB. **PCB**

**Patricia Goldman** is a 30+ year veteran of the PCB industry, with experience in a variety of areas, including R&D of imaging technologies, wet process engineering, and sales and marketing of PWB chemistry. Active

with IPC since 1981, Goldman has chaired numerous committees and served as TAEC chairman, and is also the co-author of numerous technical papers. To contact Goldman, <u>click here</u>.

**FEBRUARY 1-2, 2017** SANTA CLARA CONVENTION CENTER

> Visit our booth # 407

# **MEGTRON**

Multi-layer circuit board materials Tg 200°C, Dk 3.4, Df 0.002 @ 12GHz

# MEGTRON4S

Multi-layer circuit board materials Tg 200°C, Dk 3.8, Df 0.005 @ 1GHz

Flexible circuit board materials Dk 3.0, Df 0.0008 @ 2GHz

More information

DISTRIBUTOR IN NORTH AMERICA MATRIX USA INC. TORONTO • SANTA ANA • SANTA CLARA • CHICAGO • MINNESOTA Visit our website at www.matrixusa.us

Partnering to go beyond.

Electronic Materials Panasonic Corporation

# Final Surface Finish: How Do You Choose?

#### by Tara Dunn

**OMNI PCB**

There are so many final surface finish options to choose from today. How do you decide which is best? HASL—both tin-lead and lead-free—immersion tin, immersion silver, ENIG, OSP, and ENIPIG are the primary finishes used in PCB fabrication. Fabricators and assemblers generally work with the majority of these surface finishes to support their customers' requirements. So the question is, with all of these available, how do OEMs select their preferred surface finish?

In the past, the primary function of the surface finish was to protect the copper from oxidation prior to the soldering of components. Today's expectations also include: superior solderability, contact performance, wire bondability, corrosion and thermal resistance, and extended end use life. Designs have changed. Lines and spaces are reduced, solder types and flux chemistries are different due to no-lead requirements, the number of assembly cycles has increased, and the product may need to carry highfrequency signals. Things to think about when selecting a final surface finish:

- Does the application require tin-lead or lead-free assembly?

- Will the end environment have extreme temperatures or humidity concerns?

- What shelf life is needed? Will it be months or years?

- Volume and throughput

- Does the design have fine-pitch components?

- How many assembly cycles will be required?

- Is this an RF or high-frequency application?

- Will probe-ability be required for testing?

- Is thermal resistance required?

Once the project requirements have been identified, the surface finish options can be reviewed to find the best fit.

# **Productive Fabrication Equipment**

Bürkle North America supplies a full complement of productive equipment for fabricating printed wiring boards. From imaging through metrology inspection, Bürkle North America's equipment offering sets the standard in the industry for Imaging, Registration, Lamination, Mechanical or Laser Drill/Routing and Feature Metrology Inspection.

Contact Dave Howard for more details.

www.burkleamerica.com

Phone: 714-379-5090

#### **HASL—Hot Air Solder Leveling**

Let's start with HASL. Fifteen or 20 years ago, HASL was the universal go-to surface finish. Today, that is not at all the case. A couple of things greatly influenced this change. The first was RoHS and lead-free requirements. The second is miniaturization and the need for tightpitch components. HASL is blown from the PCB surface to remove excess; this can create uneven coverage, which makes placement of these tight-pitch components difficult at assembly. This finish is used in aerospace, defense and high-performance electronics as well as lowerend consumer markets.

#### Things to keep in mind:

- The oldest surface finish

- Tin-lead and lead-free versions are available

- Tin-lead HASL currently in limited use due to RoHS and WEEE initiatives

- Currently exempt: industrial vehicles, military, aerospace and defense, high-performance electronics

- Leaded versions are harder to source

- Long shelf life

- Not suited for fine pitch

#### **OSP—Organic Solderability Preservative**

OSP is the highest volume surface finish worldwide, with applications spanning data/ telecom, automotive and both low-end and high-end consumer products. Older versions of this chemistry were not thermally resistant and were not able to resist more than one reflow cycle. Improvements have been made to allow higher temperatures and multiple reflows without degrading. This finish does well as a selective finish. For example, when ENIG is applied as a surface finish and OSP is used selectively, it will not adhere to or stain any of the gold surfaces, so there is no need to plasma clean.

#### Things to keep in mind:

- Highest volume surface finish worldwide

- Applications range from low end to high-frequency server boards; also used in selective finishing

- The latest versions are copper selective and more thermally resistant for

high-temp, no-lead applications

- OSP is applied through chemical absorption on the copper surface; there is no metal-to-metal displacement

- Inexpensive surface finish

- Limited shelf life

#### **Immersion Tin**

Applications for immersion tin are predominantly in automotive, U.S. military and aerospace. One caution at the assembly level is the fact that pure tin thickness is lost to the copper intermetallic with time and temperature. Loss of pure tin will degrade solder performance. The first reflow exposure will dramatically reduce the pure tin thickness and deposit stress could result in tin whiskers. This is a naturally occurring characteristic of tin in direct contact with copper.

#### Things to keep in mind:

- Applications are predominately automotive, U.S. military and aerospace

- Excellent for press-fit applications (i.e., large back panels)

- All contain anti-whiskering additives, but tin whisker elimination is not guaranteed

- Low-cost, flat and suited for fine-pitch use

- Aggressive on soldermask

#### **Immersion Silver**

Immersion silver is well-suited for high-frequency applications. It has the greatest conductivity of all the surface finishes and it is flat. The signal travels to the top of the circuit reducing signal loss. This finish is often used in the data/ telecom, automotive, high- and low-end consumer and medical markets.

#### Things to keep in mind:

- Greatest conductivity of all the surface finishes; well-suited for high-frequency applications

- Applications range from low-end to high-reliability product

- Topcoats have been formulated to overcome tarnish and corrosion issues in aggressive environments

- Flat—suited for fine-pitch with excellent solderability

- Easily scratched; sliding connector limitations

- Microvoiding is something to be aware of with soldermask defined pads

#### **ENIG—Electroless Nickel/Immersion Gold**

ENIG has become one of the most common surface finishes and is often seen in aerospace and defense, medical, and other high performance markets. It is also predominant in the flex market. While this process requires many processing steps and numerous chemical analyses, fabricators run this process day in and day out with very little issue.

#### Things to keep in mind:

- Applications associated with high reliability

- Used often in the flex market

- High corrosion resistance due to nickel barrier

- Aluminum wire bondable

- No degradation between reflow cycles; can be held mid-assembly for extended times

- Potential for nickel corrosion (aka black pad) if time in gold bath is excessive

## ENEPIG—Electroless Nickel/Electroless Palladium/Immersion Gold

ENEPIG is the new kid on the block. A significant advantage to this finish is that it is gold wire bondable. Typical applications are in the medical and the U.S. military markets. This finish is expensive to process and is still relatively low-volume in the market. Fabricators are slowly bringing this process in-house as volume makes outsourcing less economical.

#### Things to keep in mind:

- Gold and aluminum wire bonding

- Applications include medical and U.S. military

- Excellent solderability

- Mitigation of black pad

- Gaining interest and acceptance in the market

There are many factors to consider when selecting a final surface finish and unfortunately, there is not a universal finish that works best for all applications. Understanding the advantages and disadvantages of each surface finish allows the designer to select the surface finish that best fits each application. Chemistry suppliers, fabricators and assemblers are all happy to offer suggestions based on their experience, take advantage of the resources available if you have questions or need assistance. **PCB**

**Tara Dunn** is the president of Omni PCB. To read past columns or to contact her, <u>click here</u>.

## Honey, I Shrunk the Circuit

Sandia National Laboratories researchers have shown it is possible to make transistors and diodes from advanced semiconductor materials that could perform much better than silicon, the workhorse of the modern electronics world.

The breakthrough work

takes a step toward more compact and efficient power electronics, which in turn could improve

everything from consumer electronics to electrical grids. Power electronics are vital for electrical systems because they transfer power from its source to the load, or user, by converting voltages, currents and frequencies. Sandia's research was published this summer in

Applied Physics Letters and Electronics Letters and presented at conferences.

## Study of Immersion Gold Processes Used for Both ENIG & ENEPIG

#### by Don Gudeczauskas, Albin Gruenwald and George Milad

UYEMURA INTERNATIONAL CORPORATION

#### Abstract

The use of electroless nickel/electroless palladium/immersion gold (ENEPIG) has been steadily increasing the past several years and benefits of the finish have now become wellknown throughout the industry. The finish provides both reliable solder joints and wire bonds. In some Asian countries where mass production is performed at many facilities, dedicated production lines have been installed for plating of ENEPIG using an immersion gold optimized for ENEPIG but not for electroless nickel/immersion gold (ENIG). In the North American market, however, many PWB facilities are producing both ENIG and ENEPIG finishes from the same plating line due to lower overall production volumes and desire to use the same immersion gold for both finishes. Most facilities have neither the room for two separate immersion golds nor the desire to tie up capital with the cost of gold for two separate immersion gold tanks. The challenge for North American manufacturers has been in choosing the proper immersion gold chemistry which can suitably deposit gold for ENIG and ENEPIG while providing a robust finish for soldering, wire bonding, and electrical contact with both finishes.

This paper presents results of a comparative study on three types of immersion golds which could be used for both ENIG and ENEPIG deposits in the same production line: standard displacement immersion gold, high efficiency immersion gold which limits nickel dissolution, and a mixed reaction immersion gold which utilizes a mild reducing agent. Comparative results for solder wetting force, solder joint reliability and wire bonding will be presented for ENEPIG. Additionally, plated samples will be examined by SEM for evidence of nickel or palladium damage from the immersion gold plating operation.

#### Introduction

Recently, it is well-known that the electroless ENEPIG process has excellent solder joint reliability (SJR) and that it has the same wire bond reliability (WBR) compared to electroless Ni/Au with thicker Au (ENAG) process, even if

the electroless Au thickness is between 0.1 to 0.2 $\mu$ m. Past studies have examined the performance of ENEPIG<sup>[1,2]</sup>. The current IPC EN-EPIG specification (IPC-4554 Amendment 1) calls for gold thicknesses between 1.2  $\mu$ in minimum at 4 sigma below the mean and 2.8  $\mu$ in maximum, and some specific customer requirements call for even thicker gold. It has been found that thicker deposits of immersion gold might lead to nickel corrosion with EN-EPIG if the dwell time in the immersion gold solution is too long.

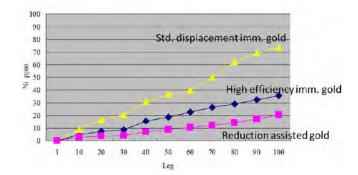

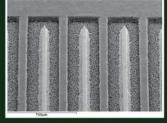

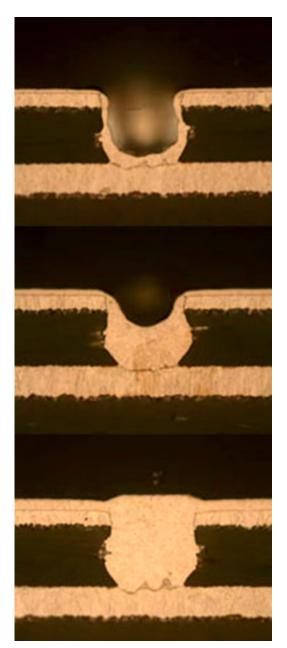

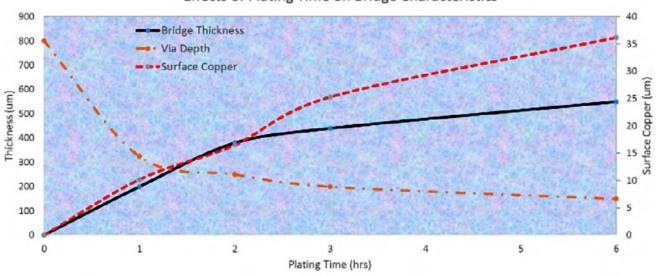

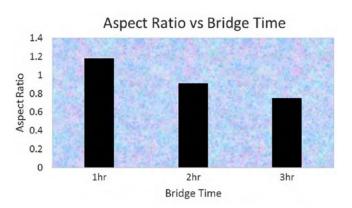

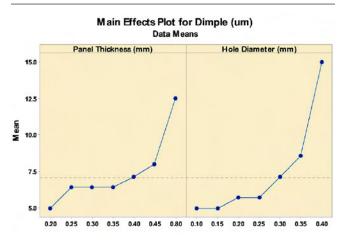

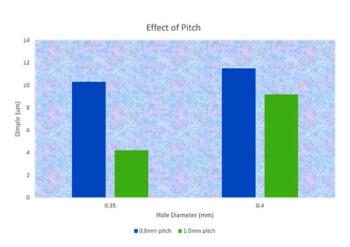

The goal of this study was to examine the performance of ENEPIG using three different types of immersion gold: standard displacement immersion gold, high efficiency immersion gold, and reduction assisted immersion gold. The three types of immersion gold dissolve corresponding different amounts of nickel while the gold deposits as shown in Figure 1 using ENIG. The high efficiency immersion gold dissolves approximately half the amount of nickel from that of the standard displacement immersion gold while the reduction assisted gold dissolves approximately 60 percent of the nickel dissolved from the high efficiency immersion gold solution. Later studies will compare results for these immersion golds with ENIG only.

Examination methods in this study included solder wetting balance tests, gold sire bonding tests, cross section analysis for nickel corrosion examination and for intermetallic formation after solder testing.

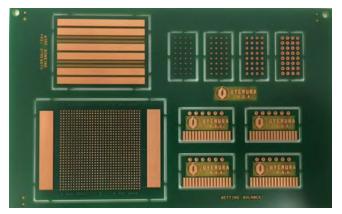

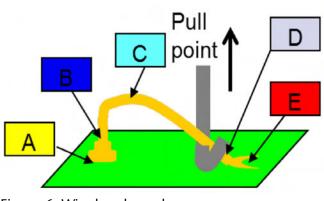

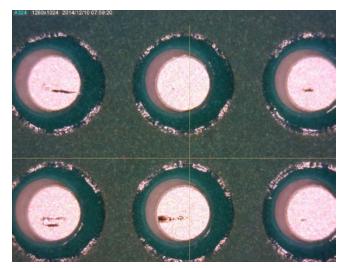

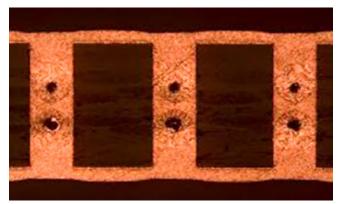

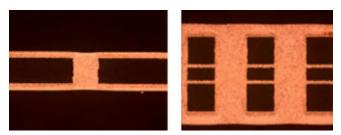

The coupons used in this study consisted of a copper metallized and pattern plated (to 25 µm) test board which was subsequently coated with soldermask as shown in Figure 2. For wetting balance tests, standard wetting balance coupons with 36 mm wetting area were used. Specific BGA pads of 0.7 mm diameter connected to a ground plane were used for cross-section examination of nickel corrosion. Two BGA pads in each array were connected to a ground plane containing 0.375 in2 area giving a 629:1 area ratio which has been shown to help cause excess nickel corrosion in the past<sup>[3]</sup>. A wire bonding coupon was used for wire bonding tests. The test coupon is shown in Figure 1. This substrate was plated with ENEPIG by using plating chemicals commercially available from C. Uyemura & Co., Ltd. The ENEPIG plating process is shown in Table 1.

| Process          | Chemical                     | Тетр      | Time         |  |  |

|------------------|------------------------------|-----------|--------------|--|--|

| Cleaner          | Mild acid                    | 40 deg. C | 5 min.       |  |  |

| Etching          | Persulfate                   | 25 deg. C | 2 min.       |  |  |

| Pre-Dipping      | 3% sulfuric acid             | R.T.      | 1 min.       |  |  |

| Activator        | Palladium-type               | 30 deg. C | 2 min.       |  |  |

| Electroless Ni-P | Mid Ni-P                     | 80 deg. C | 25 min.      |  |  |

| Electroless Pd-P | Pd-P (P=3%)                  | 66 deg. C | 6 - 9 min.   |  |  |

| Immersion gold   | Conventional Imm. Gold       | 85 deg. C | 12 - 30 min. |  |  |

| Immersion gold   | High Efficiency Imm. Gold    | 80 deg. C | 15 - 45 min. |  |  |

| Immersion gold   | Reduction assisted Imm. Gold | 80 deg. C | 5 - 13 min.  |  |  |

Table 1: ENEPIG plating process.

Figure 1: Depiction of nickel concentration in the immersion gold solutions after approximately 0.25 MTO comparing the three different types of gold plating processes used with ENIG.

Figure 2: Test board showing wetting balance coupons, BGA array and wire bond array.

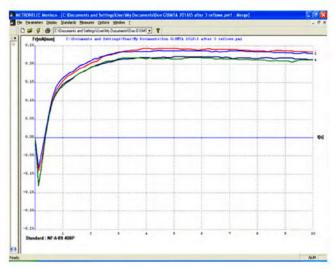

Thickness results were recorded using a Seiko SEA-5120 Element Monitor MX XRF. Gold deposit thicknesses were targeted for the lower and upper ranges of the IPC-4556 Amendment 1 specification. The cross-section images of BGA pads were observed using a JEOL JSM-6010LA SEM. Wetting balance coupons were tested in an as-plated condition and after 3x reflow at 255°C maximum temperature using a Heller 1088 reflow oven. Solder wetting balance testing was performed using a Metronelec Menisco ST 50 wetting balance with IPC test flux #1 using SAC305 solder at 255°C. Wire bond coupons were first baked at 175°C for 16 hours in a Fisher Isotemp 400 series oven. The wire bond coupons were subsequently argon plasma cleaned prior to wire bond tests. Wire bond testing was performed at Fast Semiconductor Packaging LLC (Anaheim, CA) using the equipment and conditions shown in Figure 3.

Measured thicknesses are shown in Table 2.

#### Solder Wetting Balance

Solder wetting balance test results are shown in Table 3.

| Equipment     | K&S 4524   |        |  |  |  |

|---------------|------------|--------|--|--|--|

|               | Bond 1     | Bond 2 |  |  |  |

| Temp. Setting | 150        | 150    |  |  |  |

| Temp Actual   | 150        | 150    |  |  |  |

| Power (mW)    | 2.54       | 3.01   |  |  |  |

| Time (ms)     | 3.0        | 3.0    |  |  |  |

| Force (g)     | 3.0        | 3.5    |  |  |  |

| wire size     | 1 mil gold |        |  |  |  |

Figure 3: Wire bond conditions.

|        | Sample                       | Avg. Au | Avg. Pd | Avg. Ni |

|--------|------------------------------|---------|---------|---------|

| Sample | Description                  | thk. u" | thk. u" | thk. u" |

| 1      | Red. assisted immersion gold | 2.94    | 9.39    | 217     |

| 2      | Red. assisted immersion gold | 1.59    | 7.05    | 224     |

| 3      | Std. displacement imm. gold  | 2.79    | 7.56    | 224     |

| 4      | Std. displacement imm. gold  | 1.49    | 7.77    | 206     |

| 5      | High efficiency imm. gold    | 2.98    | 4.82    | 204     |

| 6      | High efficiency imm. gold    | 1.27    | 6.35    | 187     |

Table 2: Deposit thicknesses in microinches.

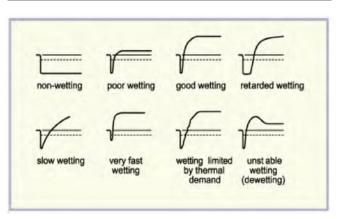

Solder wetting curves were compared to the standard curves shown in Figure 4 while a typical curve from the testing (Sample 4, standard immersion gold at 1.49  $\mu$ in) is shown in Figure 5. Solder wetting times and final wetting forces were excellent for samples tested with good wetting observed as described in the depiction figure. Interestingly, the wetting times decreased in all cases after the 3x reflow exposure. Final wetting forces were all above 0.20 mN/mm. The reduction assisted immersion gold samples showed some of the lowest wetting times while the standard immersion gold samples exhibited the longer wetting times.

#### Wire Bond Testing

Previous work performed by IPC committee members in the writing of IPC-4556 involved a large round robin test program whereby several

Figure 4: Wetting balance curve depictions.

|        |                            | Gold    | Solder wetting | Final wetting<br>Force mN/mm<br>0.25 |  |

|--------|----------------------------|---------|----------------|--------------------------------------|--|

| Sample | Condition                  | thk. u" | time, sec.     |                                      |  |

| 1      | High Eff. Gold as plated   | 2.94    | 0.31           |                                      |  |

| 1      | High Eff. Gold - 3 reflows | 2.94    | 0.20           | 0.25                                 |  |

| 2      | High Eff. Gold as plated   | 1.59    | 0.27           | 0.23                                 |  |

| 2      | High Eff. Gold - 3 reflows | 1.59    | 0.26           | 0.23                                 |  |

| 3      | Std. Displ. as plated      | 2.79    | 0.64           | 0.25                                 |  |

| 3      | Std. Displ 3 reflows       | 2.79    | 0.42           | 0.25                                 |  |

| 4      | Std. Displ. as plated      | 1.49    | 0.38           | 0.25                                 |  |

| 4      | Std. Displ 3 reflows       | 1.49    | 0.36           | 0.23                                 |  |

| 5      | High Eff. as plated        | 2.98    | 0.59           | 0.24                                 |  |

| 5      | High Eff 3 reflows         | 2.98    | 0.25           | 0.26                                 |  |

| 6      | High Eff. as plated        | 1.27    | 0.40           | 0.22                                 |  |

| 6      | High Eff 3 reflows         | 1.27    | 0.32           | 0.22                                 |  |

Table 3: Solder wetting balance test results.

Figure 5: Wetting balance test results, sample 4 after three reflows.

Figure 6: Wire break modes.

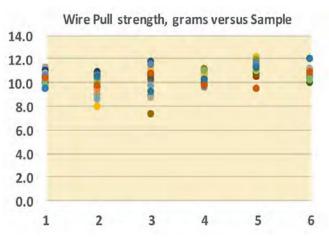

ENEPIG deposits of varying gold thicknesses from various suppliers were wire bond tested. It is believed the samples for the IPC study were not baked to simulate die attach and this current study attempted to determine if any effects of baking at 175°C for 16 hours were seen on gold wire bond results when using different types of immersion gold. A depiction of the typical wire break modes is shown in Figure 6. Ideally, wire breaks at locations B, C, and D are preferred. Wire breaks at position A and E would indicate a poor bond between wire and substrate. Results for the current study are shown in Table 4 and Figure 7, respectively. Despite heat aging, all results appeared acceptable, well above the 3-gram pull strength minimum. The standard displacement immersion gold sample with

| Sample                     | Mean | Min | Max  | Std. dev. |

|----------------------------|------|-----|------|-----------|

| 1-Red. Assisted thick gold | 10.3 | 9.4 | 11.2 | 0.48      |

| 2- Red. Assisted thin gold | 9.9  | 7.9 | 10.8 | 0.78      |

| 3-Std. Disp. thick gold    | 10.2 | 7.2 | 11.7 | 1.07      |

| 4-Std. Disp. thin gold     | 10.3 | 9.5 | 11   | 0.47      |

| 5-High eff. thick gold     | 11.0 | 9.4 | 12   | 0.58      |

| 6-High eff. thin gold      | 10.7 | 9.9 | 11.9 | 0.44      |

Table 4: Wire bond test result data for the six samples.

Figure 7: Wire bond data, 20 points per sample.

thick deposit showed lower minimum wire pull strength and higher variation in values when compared to the other samples.

Wire breaks in all tests were in the wire either just above the first bond or just above the second bond (modes B or D). No failures were seen at the wire/substrate interface (modes A or E).

#### **SEM Examination of the Deposits**

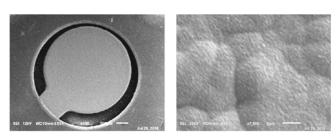

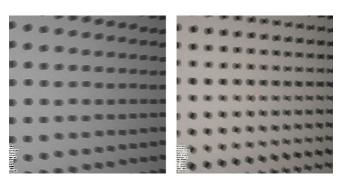

Figure 8 shows the ENEPIG deposit topdown. In general, the palladium and gold uniformly coat the electroless nickel.

Experience has shown that attempts at obtaining very thick gold with ENEPIG using a standard displacement immersion gold results in some damage in the electroless nickel layer below the electroless palladium deposit. Of the three deposited metals the electroless nickel is the least noble. Any access the immersion gold may find to the nickel will result in nickel dissolution into the immersion gold solution. Excess dwell time in the immersion gold solu-

Visit us at BOOTH # 3701

## The very best in PCB supplies and equipment

Panasonic Multilayer & Flex Laminates

High Quality ED Copper Foils

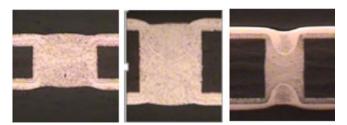

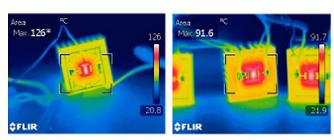

1-800-668-5447 • www.matrixusa.us TORONTO • SANTA ANA • SANTA CLARA • CHICAGO • MINNESOTA • OSAKA tion may dissolve enough palladium which may allow a pathway for the gold to attack the nickel deposit. Lateral attack of the nickel underneath the palladium has been seen in some cases where the immersion gold layer has become very thick. The resultant lateral nickel attack in extreme cases may cause delamination between nickel and palladium, especially after wire bonding. The delamination results in wire lifting and connection failure. Figure 9 shows the lateral corrosion from an ENEPIG deposit which contained 5.1 µin of gold and 3.4 µin of palladium. The gold used in this instance was the standard displacement process.

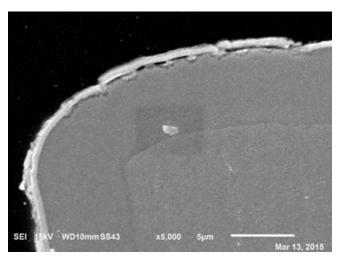

SEM cross section examination was performed for the three samples with thick gold to detect any deposit damage from the immersion gold reaction.

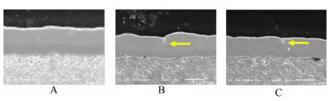

Figures 10 and 11 show cross-section images from the different deposit at the BGA pad edge

Figure 8: SEM images top-down of the ENEPIG deposit at 100x, 7500x.

Figure 9: Example of ENEPIG corrosion under the gold and palladium deposit at 5000x.

and pad center. The BGA pad was connected to the ground plane. In these three examples, the thicker gold deposit was examined for each of the three different types of immersion gold solutions. The BGA pad edges showed no nickel corrosion. The BGA pad center showed no corrosion for the reduction-assisted immersion gold while small corrosion spikes were seen with both the standard immersion gold and high efficiency immersion gold. The small corrosion spikes seen are not believed to be of consequence based on the wetting balance and wire bond data collected in this paper but can be considered a process indicator. No corrosion spikes were seen from any of the samples with thinner gold deposits.

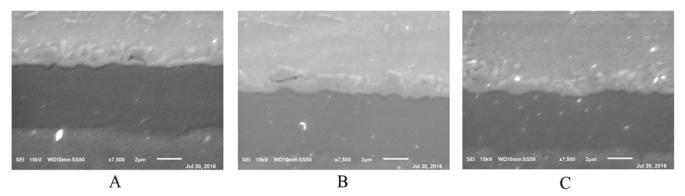

While wetting balance testing showed excellent wetting time and wetting force, cross sections were performed on the solder samples from the three thick immersion gold deposits to examine the intermetallic formed. In all cases a uniform, continuous intermetallic layer was observed as shown in Figure 12.

Figure 10: Cross-section on BGA pad edge at 5000x.

- A Reduction assisted thick immersion gold

- B Standard immersion thick immersion gold

- C High-efficiency thick immersion gold

Figure 11: Cross-section on BGA pad centers at 5000x.

- A Reduction assisted thick immersion gold

- B Standard displacement thick immersion gold

- C High-efficiency thick immersion gold

New ground-breaking CAM Software

For Rigid, Flex and HDI PCBs

- New Graphical User Interface with Workspaces

- Optimal performance using Parallel Processing

- Multi Job Processing via load balanced Sessions

- Support for Gerber version 2 (X2) format

Read more -----

Multi Core

64

Visit us in

**Booth 3532**

## Integr8tor Automated data entry and design analysis

- Ucamco's 9th Generation Sales & Engineering Tool

- Field proven with more than 250 installations in daily production

- Seamless integration into any environment

Read more

🖷 SOFTWARE PHOTOPLOTTERS DIRECT IMAGERS NEWS SERVICES COMPANY DOWNLOADS CONTACT

gbr

For more information please contact info@ucamco.us, call (415) 508-5826 or check out our new website at www.ucamco.com

Figure 12: Cross-section examination of the intermetallic formed after wetting balance test, 7500x.

- A Reduction assisted thick immersion gold

- B Standard immersion thick immersion gold

- C High-efficiency thick immersion gold

#### Conclusions

Solder wetting balance tests showed that the reduction assisted immersion gold process yielded the fastest wetting times while the standard displacement immersion gold showed slightly lower wetting times. All final wetting forces were excellent regardless of heat exposure from 3x reflows.

Wire bond testing showed very good results from all six samples with higher standard deviation observed for the standard displacement immersion gold with thick deposit. Average wire bond values were well above the 3-gram minimum with average readings all above 9 grams.

Cross section analysis of the plated samples showed some small corrosion spikes in the standard displacement and high efficiency immersion gold with no such corrosion spikes seen in the reduction assisted gold deposit. It is thought that the corrosion spikes, if present in higher amounts, would affect solder wetting and wire bond results and could be used a process check for production considerations.

Future data presentations will include the performance of the three immersion gold types with gold thicknesses at the high end of the new IPC ENIG specification. Solder testing and cross-section analysis will be performed. **PCB**

#### References

1. Yukinori Oda, Masayuki Kiso, Akira Okada, Kota Kitajima, Shigeo Hashimoto, George Milad, Don Gudeczauskas, *41st International*  *Symposium on Microelectronics,* Providence, RI, Nov 2008.

2. Donald Gudeczauskas et al, 39th International Symposium on Microelectronics, October 8–12, 2006, San Diego.

3. Snugovsky, P., Arrowsmith, P. & Romansky, M., *Journal of Electronic Materials* (2001) 30: 1262. doi:10.1007/s11664-001-0159-z.

This paper was originally presented at SMTA International 2016 in Rosemont, IL, USA, and published in the proceedings.

**Don Gudeczauskas** is vice president, Uyemura's technical center in Southington, CT USA.

**Albin Gruenwald** is technical service representative, Uyemura's technical center in Southington, CT USA.

**George Milad** is national accounts manager for Technology, Uyemura's technical center in Southington, CT USA.

# Direct Image Solder Mask

# **EMP110 DI**

Carapace<sup>®</sup> EMP110 DI is the next generation in Liquid Photoimageable Soldermask for Direct Imaging.

- Suitable for Laser and LED Direct Image Systems

- Versions available for single, dual and multiple wavelengths

- Low Exposure Energy

- Fine Solder-dam Resolution (50 micron, 2mil)

- High Chemical Resistance to ENIG & Sn Processes

- Screen-print and Spray

- Halogen-free, RoHS and fully REACH compliant with no TGIC or other SVHC content.

www.electrapolymers.com

Optimised radiation curing characteristics deliver high levels of through-cure and straight side-walls at low energy levels without compromise in surface tack or chemical resistance.

#### Aismalibar on Markets, Materials, and the Increase in Copper Prices

As a European laminate provider specializing in insulated metal substrates and thermal management, Aismalibar is often put in the demanding position of catering to some of Europe's toughest customers, including the automotive industry. Pete Starkey and Barry Matties caught up with Director General Eduardo Benmayor at electronica recently.

#### IBR Optimizes Incoming Customer Data Handling using Ucamco's Integr8tor

IBR Leiterplantten has optimized their data handling by implementing Ucamco's Integr8tor. IBR Leiterplatten is not just a typical online shop. They are a medium-sized family company staffed by a very friendly and capable team of experts ready to tackle any printed circuit board project, now more than ever.

#### A Scientific Response to Mr. Laminate Tells All

We read with interest Doug Sober's recent Mr. Laminate Tells All column, "The Certification of IPC-4101D Polyimide Base Materials: Buyer Beware." The article raises interesting questions about the IPC 4101 classification system, primarily, how is a pure resin defined?

#### New Tools Mean More Designer Control for High-Speed PCBs

In the last hour of the electronica exhibition in Munich, Pete Starkey got the opportunity to sit down with Martyn Gaudion, managing director of Polar Instruments. They discussed the changing state of PCB design, and how the newest software tools allow PCB designers and engineers to have more control when designing high-speed PCBs.

#### **<u>CIPSA Circuits Invests in Orbotech</u>** Nuvogo 780 and Additional Fusion 22

Orbotech Ltd. has announced that CIPSA Circuits, a European PCB manufacturer and long-time customer and technology partner of Orbotech, has invested in a Nuvogo 780 Direct Imaging (DI) solution, plus an additional Fusion 22 AOI System to further increase overall productivity.

#### Doosan Electro-Materials BG Signs Distribution Agreement with Arlon EMD

Doosan Electro-Materials BG and Arlon EMD have reached an agreement whereby Arlon EMD has distribution and sales rights in North America for Doosan's DS600 flexible copper clad laminates, as well as Doosan's high-Tg FR-4 and halogen-free laminate and prepreg product lines.

#### Rogers on the Booming Wireless Infrastructure Market

With the advent of 5G and next generation antennas, the already booming wireless infrastructure market is slated for continued growth through 2021, and as the primary material supplier for this sector, Rogers Corp. must continue to meet the technological demands of the Verizons and AT&Ts of world.

#### <u>Let's Talk Testing: Are You Getting</u> <u>What You've Asked for?</u>

A lot of things are taken for granted nowadays. Even in our everyday lives, we order things, but are we always getting exactly what we've ordered? What we've paid for? Maybe...hopefully...but maybe not. In the testing world, we call this double-checking "supplier surveillance."

#### Ladle on Manufacturing: Making Suppliers Work for You

Every company has its own way of doing things. For some, the engineering team develops a detailed specification for the equipment they would like to purchase and this is put out to multiple suppliers for tender, along with full documentation for the commercial terms that will apply to the purchase.

#### **Rogers Launches Laminates for Automotive Radar Sensor Applications**

Rogers Corporation announced the latest addition to its RO4000® Series thermoset circuit materials: RO4830 high-frequency laminates. RO4830 laminates offer 76-to-81-GHz auto radar sensor designers a lower-cost-but-performance-competitive option.

# Don't Let Your Temperatures Rise

## Let ROGERS' Thermal Management Solutions Keep You Cool

COOLSPAN<sup>®</sup> TECA Film • 92ML<sup>™</sup> StaCool<sup>™</sup> Laminates • ML Series<sup>™</sup> Laminates & Prepregs

Heat can be damaging, especially when it is not managed. That's why Rogers Corporation invested so much time and energy into creating an array of material-based thermal management solutions to keep heat rise to a minimum in printed circuits. From automotive circuits to LED modules to power supplies, ML Series laminates and prepregs effectively conduct heat away from the source, while COOLSPAN thermally & electrically conductive adhesive (TECA) materials enhance the thermal management of new and existing designs. And for that extra cooling edge, 92ML StaCool laminates feature a thermally conductive metal bottom plate to enhance the heat dissipation.

| Product | Thickness | Thickness Conductivity Impedan | Thermal<br>Impedance, | Tg, C | CTE (Z-Axis),<br>ppm/C                                                             |     | Dk,<br>1MHz | Df,<br>1MHz | Breakdown<br>Voltage, | Flammability |

|---------|-----------|--------------------------------|-----------------------|-------|------------------------------------------------------------------------------------|-----|-------------|-------------|-----------------------|--------------|

|         |           |                                | C-cm2/W               |       | <tg< th=""><th>&gt;Tg</th><th>0.00000000</th><th></th><th>kVAC</th><th></th></tg<> | >Tg | 0.00000000  |             | kVAC                  |              |

| 92ML    | 8mils     | 2.0                            | 0.52                  | 160   | 22                                                                                 | 175 | 5.2         | 0.013       | >50                   | HF V-0       |

Don't let your temperatures rise. Use Rogers' thermal management solutions.

Advanced Connectivity Solutions www.rogerscorp.com/acs

USA - AZ, tel. +1 480-961-1382 EUROPE - BELGIUM, tel. +32 9 235 3611

# Plating and Surface Finish: The Challenges to Electrical Test

**by Todd Kolmodin** GARDIEN SERVICES USA

#### Plating

Plating and surface finish applications are not without their own set of challenges but these manufacturing processes also affect the electrical test theatre. Microvias, high-aspect ratio plate quality, and surface finish all have their own challenges in ET.

Let's face it, the largest challenges regarding plating involve the detection of voids. Whatever type they may be is insignificant in ET as the detection is foremost the main focus. Unfortunately, with standard ET detection processes many partial voids go undetected. This also can be said for a barrel that is voided outside of the electrical test signature.

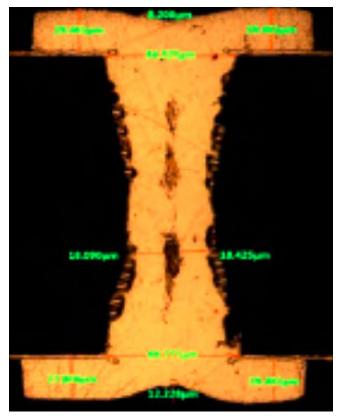

The undetected partial void is usually the "taper plate" or "narrowing" void. These defects usually have adequate plating near the annular

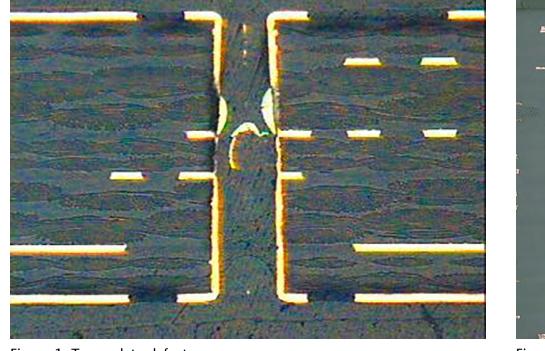

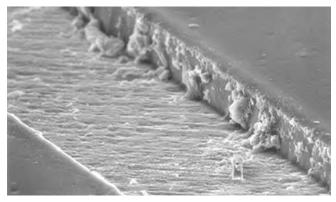

rings towards the outer layers but then narrow as they reach the center of the barrel. Figure 1 shows a typical taper plate defect.

This type of defect usually will not fail the standard ET continuity test. There is sufficient plating in the barrel to pass the electrical signal within the continuity threshold (usually 10–20 ohms depending on performance class). For the capture of anomalies such as this it is recommended that a 4-wire Kelvin sampling test be performed. This type of continuity test is designed to capture minute fluctuations in barrel resistivity. These measurements are in the milliohm (mO) range.

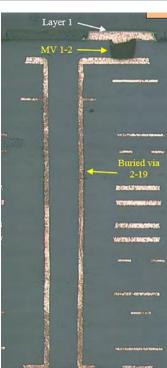

Microvias pose another challenge to ET. Usually these are buried (manufactured in the sub-part level) and have no direct landing pad accessible from the outer layer. In Figure 2, we

Figure 2: Microvia void.

Figure 1: Taper plate defect.

# **PSR-4000 HS2W** HIGH HEAT CONDUCTIVE SOLDER MASK

10 times higher thermal conductivity than standard solder resist

Phone [775] 885-9959 • www.taiyo-america.com • info@taiyo-america.com

Figure 3: Microvia barrel (outer layer).

see an example of a buried microvia that has voided. In this example, we see that there is only an annular ring termination on layer 1. This is shown in Figure 3. In this case the electrical signature is passing through the subpart (layers 2–19). In many cases this type of net has final terminations of the electrical net in different locations on either layer 1 or 20. This specific void may not be detected, as the landing pad on layer 1 in the example may be deemed a mid-point and thus be optimized out. This defect would be captured during functional test as that point in Figure 3 may be used as a signature validation or In-Circuit Test Point.

#### **Surface Finish**

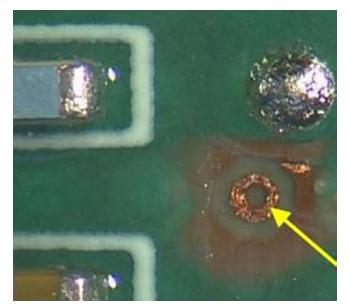

With today's final surface finishes on modern PCBs, the challenge for ET is to make sure defects are detected without scrapping the board in the process. While it has always been a ballet to successfully test the circuit board without damaging it, the more modern finishes make it much more difficult. Back in the day it was just plated holes and HASL (hot air solder leveling). This is extremely robust and in the unfortunate event of significant test marks it could be run back down the line and reflowed. Today that is far from the norm.

Today the most challenging finish for ET to successfully test is immersion silver. This deli-

Figure 4: Witness mark 1.

Figure 5: Witness mark 2.

cate finish carries the high solderability characteristic but is usually applied very thin due to cost. Electrical test probes from either fixture testers or flying probes can unfortunately leave unfavorable witness marks. In the worst case, they can break through the finish exposing the copper landing pad below. In some cases, although rare due to via capping, these boards can be reworked. In most cases, if significant witness marks are made, the board will be scrapped.

ENIG and other gold finishes take up the remainder of the surface challenges. The same hazard exists here with damage to the finish.

## HOW HAS **pluritec** CONTINUE TO STAND THE TEST OF TIME FOR MORE THAN 47 YEARS?

## WE MAKE TIME FOR OUR CUSTOMERS.

## PLURICUT AUTOMATES 8 PROCESS STEPS!

X-ray measure Inner layers, Optimize Data/Scaling & drill tooling, Flash Rout, Bevel Edges & Corners, Panel thickness measurement, Image Barcode or Readable text and Statistical Data collection.

### **Ö 8 PROCESS STEPS UNATTENDED > 2-3 MINUTES PER PANEL. TICK-TOCK!**

## MULTISTATION - EVO AUTOMATES

Onboard barcode reader manages multiple job data with scaling, vision alignment, tool management (1680+) for up to 18 panels/jobs per load.

### **O HOURS OF UNATTENDED 2ND/3RD OVERNIGHT OPERATION. TICK-TOCK!**

## **ECOSPRAY** AUTOMATES

Double-sided Mask/Legend coating of **4 different panels/jobs** with **4 different currently used materials**, tack cure and ready for imaging in 25 minutes!

#### **© CONVERTING HOURS OF WAITING TO MINUTES. TICK-TOCK!**

APEX EXPO IPC 2017 Booth 3600

Interested in making time and money? Click here. Tick-tock!

www.pluritec.com | info@pluritec.com

Figure 6: Witness mark 3.

Although in some cases it also can be reworked, customer/industry requirements may disallow the rework. Again, in this case the board would be scrapped. Figures 4–6 are examples of witness mark damage.

Combating excessive witness marks can be a challenge. With fixture testers, there are multiple variables that can contribute to damaging marks. A malfunctioning fixture is the most significant contributor. In these cases, a test probe can stick or become jammed which will not allow it to travel freely when compressed. The probe locks in place and drives a damaging signature into the targeted landing pad. Second, the actual pressure used by the machine itself can contribute to the excessive marks. Therefore, it is imperative that proper set-up procedures be used when fixture testing. The time it takes to properly set up the fixture test greatly outweighs the cost and time lost scrapping an expensive board—not to mention the unhappy customer who now has a delayed delivery.

Flying probes, although not known to contribute extensively to board damage, do have their caveat as well. Improper setup or adjustments with these machines can also cause damage. The main attributes are velocity and compression. Most significant is the Z-axis velocity. When the Z-axis travels to the board surface, its speed is important as it will travel at full velocity until the board surface is detected. If this velocity is too high the inertia of the movement may be too significant for the tensile strength of the surface finish and may damage the surface upon impact. Further, once contact is made the variable of compression also may contribute. This is the further distance the probe will move towards the landing pad once contact has been initiated. Proper adjustments to these parameters are crucial to provide the desired results without leaving damaging witness marks.

As illustrated here, even mechanical and chemical processes pose challenges to ET. It's not just the cut and dried check for opens and shorts. Care and different diagnostic measures must be used to successfully validate the product without leaving an "ET was here" type of damaging mark on the board.

HAPPY NEW YEAR! PCB

**Todd Kolmodin** is the vice president of quality for Gardien Services USA, and an expert in electrical test and reliability issues. To read past columns, or to contact Kolmodin, <u>click here</u>.

#### ETRI Develops High Performance, Autonomous Vehicle Processor

Researchers from Korea's Electronics and Telecommunications Research Institute (ETRI) have developed a high-performance processor for autonomous vehicles called Aldebaran. Increased focus by the automotive and IT industries on enhancing autonomous vehicle technology has increased the market for dedicated core processors customized for autonomous vehicles. Aldebaran uses all-Korean technology and it consists of four superscalar processors and an object recognition vision engine integrated to meet all functional safety requirements as specified by ISO 26262, an international standard concerning the functional safety of electrical/electronic systems in production automobiles developed by the International Organization of Standardization (ISO).

Get the Job Done Without Breaking the Bank AND Reduce Cycle Time!

#### OS-253 Solder Stripper is a great way

to increase productivity and minimize down-time. Long-lasting bath reduces tank shut down for cleaning / makeup. Easy waste treatment minimizes time and a built-in antioxidant allows indoor storage without having to deal with oxidized copper!

Call or email us today to place your order, you will be glad you did.

### **OS-253 Solder Stripper**

- Economical

- High Capacity

- Fast

- Leaves Pristine Copper Substrate

- Fume Control

- Minimal-to-no Sludge

For over 45 years, our customers have come to rely on us for products that work extremely well. This, coupled with our commitment to personal service, is what makes us really outshine our competitors. We look forward to meeting you.

# ACID COPPER PLATING

UNDERSTANDING WHAT'S OFTEN TAKEN FOR GRANTED

#### by Michael Carano

**RBP CHEMICAL TECHNOLOGY**

#### Introduction

Electroplating a printed circuit board is by no means a trivial task. Higher layer counts, smaller-diameter vias (through-hole and blind) as well as higher-performance material sets contribute to the greater degree of difficulty with today's technology. So, process engineers pay close attention to the "softer" issues such as cathode current density, solution chemistry (copper sulfate and sulfuric acid concentration) and addition agent control (well, sometime!).

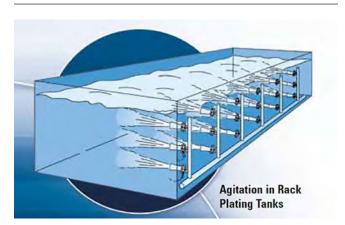

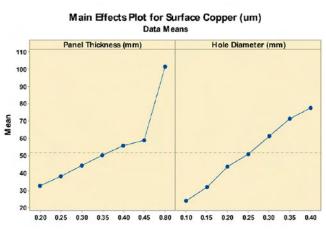

The concern here is that acid copper pattern plating of a printed circuit board has many more critical aspects that must be diligently controlled for optimum performance. These include solution agitation and filtration, anode length and placement, current distribution effects, reducing electrical resistance in the plating cell, photoresist development and controlled organic contamination in the plating solutions. These are the subjects of this article.

#### **Solution Agitation**

For uniform surface plating distribution, a homogeneous mixing of the electrolyte is necessary to avoid overplating the surface while the through-hole or blind via is being plated from the bottom up. The engineer should adjust flow rates so as to not create an excessively turbulent solution movement.

Solution agitation of the copper plating electrolyte maybe accomplished with air agitation, eductors, solution impingement and/or cathode bar movement. The main purposes of agitation have been stated many times and include:

- Elimination of solution stagnation and dispersal of reaction products

- Increase of deposition rates by mass transfer enhancement

- Dissipation of heat at electrode/solution interfaces

While the use of air agitation (supplied by a blower) was the standard method for agitating

#### WHAT IS INTEGRATE?

Integrate is a new approach to bare board PCB quality assurance. We address and are responsible for 100% of your tail end QA needs, whether it's AOI, testing, final inspection, or a combination of all three. We can provide the service in one of our service centers or fully integrate within your facility.

#### WHAT MAKES IT DIFFERENT?

**Partnership pricing.** Payment is based on product that actually passes quality assurance, not on panels produced or tested. Our success is built entirely on how successful we can help you become.

3900 jobs tooled per month

18100 orders processed per month

24,500,000 boards processed per month

Find out if our Integrate solution is right for you! www.gardien.com/why-integrate

#### ACID COPPER PLATING–UNDERSTANDING WHAT'S OFTEN TAKEN FOR GRANTED

acid copper solutions for many years, as circuit board designs have evolved into higher density patterns and smaller diameter vias, air agitation has reached its limitations. Air suffers from three main disadvantages: It has a chemical oxidative action towards solution constituents; it is electrically resistive when present as a cloud or foam of bubbles; and the general plating rate enhancement is modest despite several possible parameters for adjustment. The least appreciated characteristic is the resistivity which can lead to an increase in electroplating voltage power of 25-30% and is therefore a significant electrical cost factor. It also generates environmental pollution through its dispersion of air bubbles. In addition, these tiny bubbles can lodge into the through-holes and blind vias, leading to a reduction in plating thickness or voids.

One ideal solution (pun intended) to the need for solution agitation is to employ eductors and eliminate the use of air agitation completely. Eductor agitation is based on the Venturi principle, whereby one volume is pumped and up to four volumes are drawn in by the pressure drop, making it a highly efficient jetting system. When the system is fully submerged, no air is entrained. Such eductors are marketed by several manufacturers. Eductor agitation overcomes several of the disadvantages associated with air agitation. Air bubbles and misting are eliminated. In addition, eductor agitation provides a more uniform mixing of the plating solution. This minimizes potential dead spots in

Figure 1: Schematic of plating cell outfitted with eductors. (Source: Spray Systems Company's "A Guide to Optimizing in-Tank Agitation")

Figure 2: Actual photo of plating cell outfitted with bottom-up eductors. (Source: RBP Chemical Technology)

the cell where the air agitation is lacking. It is well known that educators provide more uniform agitation, better known as laminar flow. In contrast, air agitation provides a turbulent flow, and may only promote mixing of the solution. For quality plating results, it is preferable to have interface agitation. That is, one interface agitation is directed more at the cathode diffusion layer. This helps to reduce the diffusion layer thickness thus permitting the efficient delivery of additives and ions to the cathode surface[1].

Figure 1 shows a schematic of a plating cell outfitted with eductors. This shows the eductors pointing towards the surface to be plated. However, there are additional options available with respect to educator designs. In a second case, the eductors are pointed up from the bottom of the plating cell (Figure 2).

Both designs have extensive research and field experience that shows that with either design, surface distribution of electrolytic copper plating is greatly improved.

#### Monitoring and Controlling Carbon Content

Engineers fully understand the need for organic addition agents in the plating solution. Whether it be for acid copper or etch-resistant tin, organic chemicals are required to enhance the physical properties of the deposit, effect leveling and help minimize overplating in high current density areas. However, these organic materials, even when controlled under the most diligent protocols, do form break-down by-products over time. Essentially these breakdown products accumulate in the plating solution. There is also the potential for additional organic materials entering the plating electrolyte from photoresist leachants and pre-plate cleaner drag-in. Negative effects of the accumulated organics include rough copper-plated deposits, reduced ductility of the copper, and concerns over long-term resistance to thermal and mechanical excursions that the printed circuit device functions reliably in service over long periods of time. Higher-than-normal levels of organic break-down products will also lead to cosmetic issues.

One tool that is used to monitor organic content in plating solutions is TOC-total organic carbon analysis. Since a TOC analyzer can be used to manage the concentrations of organic material in plating solution, it can be utilized for quality management of electroplated products and the overall health of the plating solution. While it is not expected that every printed circuit board manufacturer would have its own TOC unit in-house, most chemical suppliers provide this service. What is critical for the manufacturer is to monitor the TOC content over a time interval and equate these values with end-product performance. It should be noted that not all acid copper plating additives are created equal. Therefore, one should not try to draw conclusions on organic content with values of TOC from two different suppliers.

#### **Anode Length and Placement**

The placement of the anodes in a plating cell is critical with respect to plating distribution. One should look at the anode as where the lines of flux or current is distributed into the cell and onto the cathode (the circuit board). Electricity follows the path of least resistance. That is precisely why it is often difficult to achieve optimum surface plating distribution across a printed circuit board panel. Typically, those isolated circuit features and the top of the circuit board attracts more current than other areas. Thus, these areas tend to plate to higher thicknesses than the lower current areas. The engineer's job is to find ways to reduce these current variations. Certainly, chemical and other operational parameters can be adjusted to aid distribution. However, one should not overlook the anode placement and length. As a rule of thumb, distribution and throwing power are improved if the cell design allows for a longer distance between the anode and cathode (ideally, 10-12 inches is recommended). In addition, anode length should be 4-6 inches above the lowest level of the circuit board in the plating cell.

Finally, there are additional techniques that can be used to enhance plating uniformity. One such method is the use of non-conductive shields. These shields are strategically placed in the cell to redirect current away from the perceived higher-current density areas of the circuit board. The shields can always be removed.

#### **Electrical Resistance in the Plating Cell**

While most engineers work diligently to control the chemical aspects of the electroplating process to insure optimum throwing power (surface-to-hole ratio), they often overlook other critical parameters of the process. These include resistance through the cabling leading from the power supply to the plating cell, plating rack current-carrying capacity, and additional resistances within the cell. As it stands, electroplating is governed by Ohm's law. The greater the resistances within the plating cell, the more difficult it will be to achieve uniform plating thickness distribution. If the author can use this analogy:

- Current flow (analogy) is likened to a flow of water through a hose

- Flow of water:

- GPM = pressure divided by resistance

- In other words, the longer the hose or the smaller the diameter of the hose opening, the less water you will get

Geek-a-Palooza is a social networking event for all of us electronics geeks that focuses on expanding our resources, building relationships and bringing every aspect of the local electronic industry together.

# Gearing up for an even bigger 2017!

With events in Southern California, Boston and Minneapolis, 2016 was a big year for us. We'll be back with even more events next year. Click on the button below to be notified of our 2017 events.

Notify Me!

geek-a-palooza.com

## A great big thank you to all our 2016 Geek-a-Palooza sponsors!

You are the wind beneath our wings, and we couldn't do it without you!

## Join Team Geek in 2017!

2017 will be our biggest year yet, and now is the perfect time to get in on the action.

Become a sponsor

The same can then be said about current flow to the plating cell. Current is dependent on resistance and voltage. If resistances increase, the flow of current to the plating cell is reduced.

Based on this analogy, the author prefers to design the cell with minimal distance of the cables from the power supply to the plating cell. In addition, the current-carrying capacity of the cables is critical to achieve uniform current flow and to minimize current loss. If the cabling from the power supply (rectifier) to the cell feels hot to the touch, this is an indication that there is a loss of current reaching the cathode (circuit board to be electroplated). It is wise to replace these cables on a regular basis to insure quality plating.

Finally, do not overlook the quality and material of construction of the plating racks. While stainless steel is a rugged material for rack construction, it does not have the conductivity of copper. A well-designed copper plating rack will deliver 88–92% of the current supplied by the rectifier to the cathode. Conversely, stainless steel is only 50–55% effective!

#### Filtration

The need for filtration cannot be emphasized enough, especially when plating in throughholes and blind vias. Any void in the plating in the hole caused by small pieces of contaminant causes a reduction in the area available to carry the electric current. Rejects would also be caused when insoluble debris is co-deposited on the surface or in the hole.

Flow rates are the only means of carrying solids to a filter or bringing fresh solution into contact with the particulate matter. The rate of flow is referred to as the turnover-total gallons pumped per hour in relation to the size of the tank (for example, 200 gal/hr on a 100-gallon tank equals two turnovers per hour). Dirt holding capacity is essential and can be attained with throw-away paper, or cartridges of different porosities, or filter surfaces coated with filter aid. Porosities of 100 microns down to less than one micron are typical. In practice, the average plating solution is turned over once per hour. The recommended flow rates should provide at least two complete tank volume turnovers per hour. However, to achieve the ultimate in clarity, turnovers of up to ten times per hour may

be necessary. Keep in mind that the initial flow rate is not the average flow rate. In other words, if one started at 1000 gal/hr, and cleaned or replaced the filter when the flow was reduced to 200 gal/hr, the actual average flow would probably be about 600 gal/hr, depending upon the type of filter media used.

#### Developing

Developing photoresist is one of the simpler chemical processes in the making of a PCB, yet one of the more crucial, as it defines what the circuitry will look like when the PCB is finished. Because developing is apparently so simple, it is easy to overlook its significance to the production of high quality PCBs, and to overlook the details necessary to produce high quality developing. Incomplete developing, over-developing, positive or negative foot, etc. will plague even the most experienced plating engineer.

The standard developer today is a 1% solution of either sodium carbonate monohydrate (Na-2CO3.H2O), or potassium carbonate (K2CO3). There is not much to choose from between the two, although the use of potassium carbonate has been reported to give slightly better quality developing, and have a wider process window. Potassium carbonate can be purchased in concentrated liquid form, allowing convenient feed and bleed application, without large feed tanks.

In the days when 6-mil lines and spaces were considered fine lines, using developer solutions to the point where the developing slowed dramatically and then dumping them, was an acceptable scenario. However, this modus operandi is no longer effective. Today's higher circuit density creates a washboard effect, making it more challenging to deliver sufficient amounts of developer solution to the circuit board. Therefore, manufacturers insure that tightly pH-controlled developing processes are in use. While understanding that feed and bleed systems allowing for steady pH control are critical for optimum performance, there are several other aspects of developing that are often overlooked as to their importance. One such aspect is the spray nozzles used in the developing and rinsing chambers.

Full cone and high impingement spray nozzles are most popular in conveyorized spray

RECISION IN MOT

66 6

In HDI PCB manufacturing, where customer requirements are constantly evolving, you need a solution that's both affordable and versatile in order to remain competitive. nViant brings that affordability and versatility within reach in a low-cost, high-volume HDI processing platform.

For over 40 years, ESI has been providing the laser technology and expertise needed to keep up with an industry in motion. With reliable platforms such as nViant, teamed with premier service and support, we help the world's top PCB processors meet their customers' needs for quality and accuracy.

Choose ESI as your full-service partner to stay ahead of the HDI manufacturing game.

Learn more at esi.com

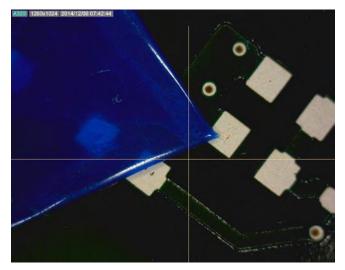

Figure 3: Developer/resist residues remaining on sidewall and surface. (Source: IPC-9121 Process Effects Handbook)

Figure 4: Plugged nozzles in developer chamber. Note uneven developing patterns on the test panel. (Source: RBP Chemical Technology)

modules for PCB processing. The advantage of the cone nozzle is its high liquid volume delivery. However, fan nozzles provide higher impact (impingement). This is highly effective especially when developing finer lines and spaces. The author wrote in a previous column[2] that high impingement fan type nozzles work very well in the aqueous development for the removal of resist and developing solution residues from the copper surface and the exposed sidewalls of the resist. A clean removal of all residues from the copper surfaces and sidewalls is required for defect-free plating and to insure the circuit trace is as uniform as possible. In addition, rinsing after developing with a minimum of 70°F water temperature is most effective in removing these alkaline residues. Figure 3 shows incomplete development due to either low pH, inadequate rinsing or insufficient developing/rinsing spray pressures.

And finally, proper maintenance of the spray nozzles in both the developing and rinsing chambers is necessary to ensure nozzles remain clean and free of resist residues. An example of what plugged nozzles will lead to is shown in Figure 4.

At this point, the operator needs to suspend the operation and either replace the nozzles or at the very least clean the machine and nozzles.

#### Summary

To deliver a high-reliability printed circuit board, engineers must not overlook or take for granted aspects of the process that have great impact on the end result. Certainly, most operators and engineers worry about controlling the wet chemistry of the plating process and imaging fundamentals such as exposure. Yet, they are often surprised and disappointed that the quality of the finished product is not meeting stringent quality requirements. Further examination will find that other aspects of the process often overlooked were not sufficiently controlled and maintained. Thus, it only makes sense that in addition to wet chemistry, other factors such as resist developing, rinsing and nozzle maintenance, resistances in the plating cell, and agitation and filtration will contribute to overall quality. Ignore these at one's peril. **PCB**

#### References

1. GABE, D.R., 2006. "Process Agitation: from air bubbling to eductor jetting," Transactions of the Institute of Metal Finishing, 84 (2), pp. 67–78.

2. <u>Primary Imaging for Pattern Plating, Part</u> <u>2: Development</u>, The PCB Magazine, June 2016.

**Michael Carano** is VP of technology and business development for RBP Chemical Technology. To reach Carano, or read past columns, <u>click here</u>.

# Six reasons why outsourcing CAM Engineering can be a great idea for you:

# ...and here is the delivered value:

|                        | In-House   | With Entelechy        |                      |

|------------------------|------------|-----------------------|----------------------|

| Availability           | 48 weeks   | 52 weeks, 24/7        | ۴۴ In ou             |

| Overhead Cost          | >30%       | 0%                    | CAM de bottlene      |

| Scalability            | Limited    | Unlimited             | working<br>can now a |

| Redundancy             | Variable   | 100% Bulletproof      | had to               |

| Operational Efficiency | Status Quo | Continual Improvement | -Thomas H            |

| Total Cost             | Fixed      | Significantly lower   |                      |

<sup>44</sup> In our company, the CAM department was the bottleneck. As a result of our working with Entelechy, we can now accept orders that we had to refuse in the past.<sup>33</sup>

-Thomas Hofmann, CEO/Owner

HOFMANN Leiterplatten

### Click here to check out our risk-free Quick Start program»

We deliver the highest quality PCB CAM and Mechanical CAD engineering services to customers around the world. We can help you beat your competition by teaming up with us.

www.entelechyglobal.com

# **Electronics Industry News** Market Highlights

#### <u>Perovskite Solar Cells Hit New World</u> <u>Efficiency Record</u>

They're flexible, cheap to produce and simple to make, which is why perovskites are the hottest new material in solar cell design. And now, engineers at Australia's University of New South Wales in Sydney have smashed the trendy new compound's world efficiency record.

#### **Printable Electronics**

The next time you place your coffee order, imagine slapping a sticker onto your to-go cup that acts as an electronic decal, letting you know the precise temperature of your triple-venti no-foam latte.

#### £10M Award Creates Compound Semiconductor Hub

A £10m award announced today puts Cardiff University at the forefront of research into cuttingedge Compound Semiconductor (CS) technologies.

#### IDC Unveils its Top 10 Predictions for Worldwide Robotics for 2017 and Beyond

IDC predicts 35% of leading organizations in logistics, health, utilities, and resources will explore the use of robots to automate operations by 2019.

#### **4G Smartphones to Surpass 1 Billion Mark in Shipments for 2016**

Worldwide smartphone shipments are expected to reach 1.45 billion units with a year-over-year growth rate of 0.6% in 2016, according to the latest forecast from the International Data Corporation (IDC) Worldwide Quarterly Mobile Phone Tracker. Although growth remains positive, it is down significantly from the 10.4% growth in 2015.

#### Nano Dimension Delivers 3D Printer to a Fortune 100 Company

Nano Dimension Ltd, a leader in the field of 3D printed electronics, announced that its wholly owned subsidiary, Nano Dimension Technologies Ltd, has delivered a DragonFly 2020 3D Printer to a Fortune 100 company for evaluation purposes.