# DESIGNOUT MAGAZINE

# Our library is the bookmobile for the 21st century.

Registered members of **my I-Connect007** have access to our ever-growing library of eBooks, which now includes a wide range of topics from DFM to thermal management.

Instead of waiting for the bookmobile, though, our users download new titles with the click of a mouse. It's pretty awesome!

#### View our eBook library

1<mark>.007</mark>e Books

# **POWER INTEGRITY BY EXAMPLE**

#### THE PRINTED CIRCUIT DESIGNER'S GUIDE TO..."

### **Power Integrity by Example**

I-007e Books

### **TOPICS COVERED:**

- Bare Cavity

- Decoupling Capacitor and VRM Effects

- Transparent Cavity

- Cavity Noise and Via-to-Via Coupling

- Reducing Via-to-Via Coupling Using Capacitors

#### MAY 2018 • FEATURED CONTENT

# DESIGNOOT MAGAZINE

## 5G: Coming to Your World Soon

We've all heard plenty about 5G lately. The transition from 3G to 4G meant a 10x increase in speed, but 5G will be at least 1,000 times faster than 4G. What does 5G mean to PCB designers and manufacturers? For this month's issue on 5G technology, we asked a variety of contributors to help us flesh it out.

10 Experts Discussion: What Does 5G Mean to Materials and EDA Tools?

by the I-Connect007 Editorial Team

18 Dan Feinberg Discusses Implications of 5G by Andy Shaughnessy

- 22 Paving the Way for 400Gb Ethernet and 5G by Chang Fei Yee

- 32 Making the Most of PCB Materials for 5G Microwave and mmWave Amps by John Coonrod

## Engineering And Providing Balanced Interconnect Solutions

nechanical environmental

electrical cost

Miraco, Inc. Manchester, NH miracoinc.com 603-665-9449

...connecting technology

SOLUTION

#### MAY 2018 • ADDITIONAL CONTENT

# DESIGNOOT MAGAZINE

#### SHORTS:

- 17 Tech Bends Light More Efficiently, Offers Wider Angles for Light Input

- 35 Design for Magnetoelectric Device May Improve Your Memory

- 44 Researchers Develop Handheld 3D Skin Printer

- 50 Hematene Joins Parade of New 2D Materials

- 56 Infrared Spectrometer on a Chip

#### **ARTICLES:**

- 60 Mark Thompson: What Designers Need to Know about Fab by Dan Beaulieu

- 64 Faster Board Speeds Demand Constraint-Driven Design by Ralf Bruening

#### **COLUMNS:**

- 8 5G: It's Kind of a Big Deal by Andy Shaughnessy

- 38 Common Symptoms of Common-Mode Radiation by Barry Olney

- 46 Hiring the Right PCB Designer by Tim Haag

- 52 Protecting PCBs from Harsh, Challenging Environments by Alistair Little

#### HIGHLIGHTS:

- **36** PCB007

- 58 MilAero007

72 Top 10 PCBDesign007

#### **DEPARTMENTS:**

- 76 Career Opportunities

- 82 Events Calendar

- 83 Advertiser Index & Masthead

## TRANSFORMING ELECTRONICS SYSTEMS DESIGN

stems

THROUGH DIGITALIZATION, ORGANIZATIONS ARE TRANSFORMING THEMSELVES TO SUCCEED IN A WORLD WHERE PRODUCT COMPLEXITY IS EVER-INCREASING AND MARKET DEMAND FOR DIFFERENTIATED FUNCTIONALITY IS AT AN ALL-TIME HIGH.

#### WHAT DOES TRANSFORMATIVE PCB DEVELOPMENT LOOK LIKE? ATTEND THE 2018 PCB FORUMS TO FIND OUT!

FIND A LOCATION NEAR YOU AT WWW.MENTOR.COM/PCB-FORUM

PCB

$\cap \cap$

## **5G:** It's Kind of a Big Deal

#### The Shaughnessy Report by Andy Shaughnessy, I-CONNECTO07

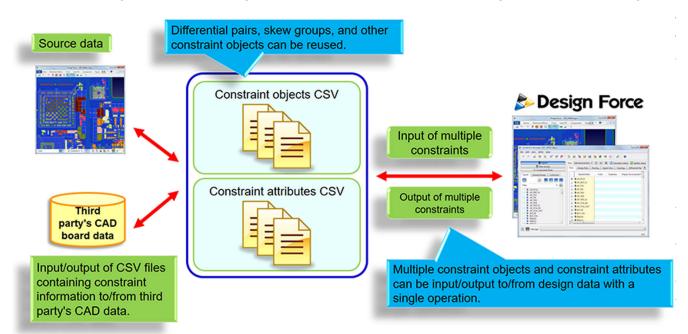

We've all had it happen: You dial a number on your cellphone, but it doesn't connect immediately. Sometimes you have to wait 10 or even 15 seconds before the other party's phone starts ringing. If you're like me, you curse at your phone, then at Verizon, and say, "They can put a man on the moon, but I have to wait 15 seconds for a phone call? This is an outrage!"

Well, help may be on the way in the form of 5G. We've all heard plenty about 5G lately. Some companies are likely to be using 5G this year, but not commercially. The first commercial 5G services probably won't be available until 2020. But behind all the hoopla, what does 5G mean to us and our industry?

The main thing to remember is that the switch from 4G to 5G is exponentially different than the move from 3G to 4G. The transition from 3G to 4G meant a 10x increase in speed; 5G will be at least 1,000 times faster than 4G. Some carriers are claiming that we'll be able to download an HD movie in less than 10 seconds. (For reference, the 3G–4G upgrade cost billions of dollars worldwide. No word on what the 4G–5G switch will cost.)

So, it's kind of a big deal. What does it mean for you and your customers?

A lot of people I've spoken with—designers, fabricators, and assembly providers—aren't sure what it's going to mean for their companies. I think it's safe to say that the majority of PCB companies are just going to wait and see how things shake out. It's difficult to build a roadmap around a technology that hasn't been implemented yet.

Many of us will be watching the 2020 Summer Olympics in Tokyo for more than cover-

age of gymnastics—NTT DOCOMO of Japan plans to launch commercial 5G services for the games. NTT DOCOMO is partnering with companies like Samsung, Huawei, Nokia, and Ericsson to have 5G up and running in two years.

Most companies working on 5G have formed alliances with other tech companies. These firms all realize that they can't implement something of this scale without strategic partnerships. Maybe our industry should try that approach more often.

For this month's issue on

5G technology, we asked a variety of contributors to help us flesh out what this all means for PCB designers and manufacturers. In our experts discussion, John Hendricks of Rogers Corporation discusses Rogers' plans to field high-speed materials for 5G applications, and Ben Jordan of Altium explains what 5G means for EDA software tool providers. Next, Technology Editor Dan Feinberg focuses on how 5G will affect our industry, and who won't be affected by this change. CF Yee of Keysight Technologies has a feature article on PAM-4 and its application in 400-Gb Ethernet to support the huge traffic volume expected with 5G. Further, John Coonrod of Rogers discusses the challenges that 5G presents to laminate manufacturers, who will have to contend with microwave frequencies below 6 GHz and millimeter-wave frequencies of about 30 GHz.

We also have columns from regular contributors Barry Olney, Tim Haag, and Alistair Little, as well as an interview with columnist Mark Thompson and an article on constraint-driven design by Zuken's Ralf Bruening.

#### Speaking of Communication...

Fabricators always ask designers to communicate with them early in the design process to help avoid DFM issues later on. But is this

even possible?

Case in point: At the recent SMTA Atlanta, the Designers' Roundtable drew a group of approximately 15 designers and design engineers. Doug Philbrick of ITS, an assembly provider, and Rick Kincaid of K&F, a fabricator (who, by the way, lost about 50 pounds and looks great), were also in attendance. Doug and Rick both mentioned that they'd like to have more communication with PCB designers early in the process.

However, almost every designer in the room said

that they never knew who was going to fabricate or assemble their boards. Most designers didn't know who was going to do the protos or volume production; a few actually laughed at the idea that a designer might know who was going to turn their design into a reality.

So, is all of this preaching about talking to your fabricator early just a bunch of happy talk? I'm curious. Do you know who is going to fabricate and assemble your designs? Let me know your thoughts on this. We may be on to something.

See you next month! **DESIGN007**

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 18 years. He can be reached by clicking here.

# Experts Discussion: What Does 5G Mean to Materials and EDA Tools?

#### Feature by the I-Connect007 Editorial Team

Whether we're ready for it or not, 5G technology is coming. While many companies are waiting to see how we're all affected by this, PCB materials providers and EDA tool vendors have no such luxury. For this issue, we spoke with John Hendricks, market segment manager for wireless infrastructure at Rogers Corporation, and Ben Jordan, director of product and persona marketing for Altium, about the challenges related to 5G and what this means for PCB designers and fabricators.

**Andy Shaughnessy:** John, could you tell us a little bit about what you do at Rogers and your thoughts on 5G?

**John Hendricks:** Rogers Corporation manufactures high-frequency printed circuit board materials. I'm a market segment manager, and that means I have responsibility for the wireless infrastructure business, globally. It's my job to identify what we need to be doing to meet both current and future needs.

And 5G has some interesting challenges. If you look at it from the PCB material point of view, in the past there was not that much change as you went from 2G to 3G to 4G. Lots of other technologies developed very dramatically of course, but in the circuit board business, not a whole lot changed in terms of what was required from materials. And the simple reason for that was that, from a hardware point of view, there were just small differences in frequencies—700 megahertz, 900 megahertz, 1.8 up to 2.5, something like that. And a power amp still basically looked like a power amp, and an antenna still looked like an antenna.

5G is interesting because, as most people know, it's split into two areas; a much bigger area, at least in the beginning, is the sub-six gigahertz market. And then you have the millimeter wave, which is 28 gigahertz. The millimeter wave presents some very dramatic changes to the material requirements because of the much higher frequency, so materials must be much lower loss. They have to be much thinner, much smoother copper.

#### www.nisteceltek.com

# eltek

a Nistec company

## Helping people live longer, healthier lives for more than 25 years.

Eltek is trusted supplier of complex PCBs for medical devices. Our manufacturing expertise ranges from implantable devices like pacemakers and neurostimulators, to insulin delivery systems and advanced medical imaging products.

Product quality and reliability are critical to success in this field. Eltek's advanced manufacturing capabilities and technical support are designed to mitigate risks and deliver products that meet and exceed the most stringent standards of the industry regulatory bodies.

For over 25 years, Eltek's PCB solutions have been helping people live longer and healthier lives.

#### Learn More

Down at sub-six gigahertz, there's not so much of a dramatic change in the electrical requirements of the materials, but one of the things that is happening is, perhaps not necessarily in the very first iterations, but certainly in newer designs that we see coming out on the horizon, there's a lot more integration between the antennas and the power components and the transceivers, and going forward even more integration with the high-speed digital parts.

So, you see much more complex multilayer printed circuit boards, and a lot more integration. You see these modular stacks starting to look a bit more like highspeed digital boards. And so, the manufacturability of the PCB becomes more critical, and the ability to make much complex multilayer more PCBs becomes more critical than it was from 2, 3 and 4G. I think that's how I would sum it up.

#### Shaughnessy: Ben, why don't

you tell us a little bit about yourself, then just give us a few thoughts on 5G.

**Ben Jordan:** Sure. My background is more digital than anything. I was an FPGA programmer before getting into the EDA space. For me, RF has always been this scary black box thing. And I know that 5G is going to affect many people, especially at the PCB design level. That's because those people don't necessarily have any knowledge or experience with doing RF PCB design or RF system-level design.

But the whole point of moving to 5G is to enable many thousands of additional devices to join the network, where the whole push for this from my point of view is so the Internet of Things could go to its next stage of evolution. There are going to be many thousands of devices needing reasonable bandwidth, a lot of them are going to be thirsty, and a lot of devices will have very, very small bits of information. So, if you read up on 5G, you read that there could be many hundreds of thousands of simultaneous connections from sensor arrays, or it will be used as a sensor network. Maybe the flagship consumer will still be mobile phones, but the same networks in our homes, in our streets, in our cities, are going to be 4G or 3G, will be completely saturated if all those different IoT sensors and services that we're dreaming up were to have to use those older technologies.

> That's really what's driving this and what's pushing bandwidth to be increased to accommodate this. What do vou do to increase bandwidth? You make much more complex modulation schemes, and you also must increase carrier frequency. So now with 5G we're going to be seeing in the millimeter wave, bandwidths up to 60 gigahertz, for example. What does that mean for PCB designers and people like me who don't know a lot about RF? It's kind of scary, if you

think about it.

I think, to a large extent, we have been relying on our chip manufacturers, companies like NXP or Broadcom and Qualcomm, to come up with the goods in a very easy-to-consume sort of package, so that a lot of those materials and a lot of the RF signal pathways are contained on a chip, and the antennas are there. One of the good things about high frequency carriers is the sizes of the antennas can shrink. One of the other things about 5G is its ability to go peer to peer. Then various nodes on the network will be able to quickly negotiate direct links and communicate peer to peer and not require a base station all the time.

Some of those bottlenecks will disappear and it will become more of a true mesh. And in doing so, we can have lower power requirements because there's less signal strength required in many instances. So that can help with the hundreds or thousands of sensor arrays or other smart devices. In terms of PCB design, reduc-

John Hendricks

ing power requirements can greatly simplify things. But it does increase other challenges for passing electromagnetic compatibility standards and certifications. That's going to be a huge challenge for a lot of the designers out there. And they'll have to learn more anyway, even if they're doing everything with a simple chip and a basic carrier printed circuit board, all the way to maybe a more specialized hub style device, like a tower or a node for aggregating connections.

Those boards are going to be the complex ones with exotic materials. But then hopefully the actual end-user devices will be simpler, because a lot more of the magic secret sauce will be on the chip, or in the package, or in the die. And in my mind, the problems are equally on the semiconductor companies as they are on actual board-level design engineers and PCB designers.

**Shaughnessy:** Right, they're supposed to start releasing commercial chips, this year and next, designed for 5G.

**Jordan:** I have a friend who is an RF engineer at a company that begins with Q. I was speaking with him just this morning, knowing I was going to join this discussion. And he said he's working on 5G right now, and it's very, very difficult for those guys doing the actual chip design and the analog front end. We'll see how well that goes.

**Shaughnessy:** One of the things that I've seen is that they're saying some of these are going to require much thicker boards. You know, they're going to demand thicker PCBs and they're going to have higher aspect ratios and it is going to be a lot harder for everybody, but harder for the fabricator to put these boards together.

John, have you seen that in your findings?

**Hendricks:** Yes, in truth we see a lot of people trying a lot of different solutions for the same type of problem. But there are some common threads that run through them, including a greater degree of integration that is leading

to more complex, thicker PCBs. We're talking about boards that can be 10, 14, 16, 18, or 20 layers, which we wouldn't have seen in the past on previous generations of mobile communications or what have you. So yes, you do see that complexity, and you do see much more challenge on the PCB manufacturing side, and that's what I was referring to when I was talking about the stacks starting to look like more complex high-speed digital boards than they have in the past.

**Shaughnessy:** As far as materials go, is it going to require a whole different set of new materials?

**Hendricks:** I think that depends on whether you are talking about the sub-six gigs or the millimeter wave. The sub-six gigs can broadly work with the materials that are available today. What happens at 28 gigs and higher is that you start to require, for example, extremely smooth copper. What happens in

What happens at 28 gigs and higher is that you start to require, for example, extremely smooth copper.

the millimeter wave range is that as the materials become thinner, which is simply a function of the smaller wavelength, then it's more than just having to have just a low loss dielectric. The components of insertion loss on a microstrip circuit are both conductor-based and dielectric-based, and as you get thinner the copper component of that loss becomes more important. And that's driven primarily by the smoothness of the copper, because at very high frequencies you have the skin effect and the current travels along the bottom of the copper, so things like the copper foil roughness become more important. When you start having smooth copper, that means that you have challenges with copper bond and peel strength.

With the millimeter wave, you certainly start to foresee more material challenges than you see at lower frequencies.

**Jordan:** I think this really does tie into the CAD side as well, because if someone doesn't have a lot of experience and knowledge, we always say, "Work with your fabricator." A lot of fab-

ricators are going to struggle with this stuff, and there will be a few leading-edge ones, and it might be more suitable for people working on 5G apps and design to work more with the materials company first than with the fabricator. I can foresee that we're going to need improved capabilities in layer stack planning, and maybe even some kind of simulation capability for things more around the mechanical limitations of laver stacks.

People already do thermal

analysis on their circuit board designs, they do impedance control calculations and use 2D and 3D field solvers to make sure their layer stack is going to function as desired at RF and highspeed digital edge rates. But there's going to be an increasing number of people who have a great idea but don't know the mathematics or analysis techniques behind getting something to work with an appropriate layer stack that's affordable to manufacture.

Ben Jordan

With all those tradeoffs, on the CAD side, we need to introduce capabilities in layer stack planning that will help people making those tradeoffs and reuse known good layer stacks. Maybe it would be good for us to partner with a company like Rogers and come up with sample layer stacks that people can reuse. You know, if you build it this way, specify it this way, you'll have an easier time getting your design to production.

Hendricks: Sure. At Rogers, we have a two-

the electrical designers, the manufacturers, and the material suppliers. We effectively have to work together.

**Jordan:** Collaboration is really the name of the game, isn't it?

Hendricks: Yup.

**Patty Goldman:** How often does that collaboration happen?

**Hendricks:** There's often this old-fashioned traditional

approach where the electrical designer designs a PCB and then goes to a PCB manufacturer and the PCB manufacturer says, "I wouldn't have designed it that way." I guess there's always an element of that in it. We don't often have three-way partners or three-way meetings, but there is a set of three-way communications. We talk closely to the PCB manufacturers and the OEMs equally, basically.

**Goldman:** I asked that because we hear that so often on all sorts of different subjects that "if only they could let us know first and we could all work together it would be so much better."

**Hendricks:** Yeah. It never goes completely smoothly (laughs).

**Stephen Las Marias:** Do you think these 5G challenges will have an impact on the PCB assembly side?

# VERIFY **OPTIMIZE** ANALYZE PREPARE PANELIZE COMMUNICATE DOCUMENT

## **Ensure PCB Manufacturing Success!**

**CAM350**°

Verify and Optimize PCB Designs for Successful Manufacturing.

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

©2016 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB design post processing needs.

#### Visit downstreamtech.com or call 800-535-3226

**Jordan:** I think the issues with assembly remain the same for any kind of wireless technology. There's going to be DFT; it's going to create new problems and new opportunities, again because it's new physical connectivity and modulation schemes, and new rules from the FCC and CE and Europe and others, for making sure products don't cause problems. And all of that impacts assembly, in my mind anyway, because assembly is the first task of that final stage of production. The second half of that stage, which is done typically in the assembly process, at the end, is the test. And designing for test is going to have new challenges with 5G. I mean, how are you going to test that your devices are too chatty when it's supposed to be functioning and not using too much bandwidth on a network in a certain geographical region where there could be 1,000 other devices?

How do we test for that? And how do we design the PCB at those millimeter wave frequencies; the probe effect is going to be a huge problem. You know, the probe effect is that by measuring something you affect how it operates. So how do you measure? And that happens at those kinds of frequencies. So, the assembly houses are going to have to develop and buy new test equipment that's going to ensure these products pass muster. Not just functionally, but that they pass the rules. Maybe I have a naïve idea of that, but that's just my two cents on that question.

**Las Marias:** I think you're right, Ben. Thank you for that.

**Shaughnessy:** Happy, is there anything that we're missing? What do you think about the 5G?

**Happy Holden:** At Hewlett Packard, we typically would do testing for up to 800 gigahertz. When you're designing and building boards, and we have to measure something that's in 800 gigahertz, you have to be 10 times better. And so, RF design and RF materials were always a big headache, but that's where HP made a lot of money, because not too many people could build this test equipment. Now this kind of specialty, rather than being with the OEMs, is going to come down to common board fabricators and board assemblers that may not have the manpower, the equipment, the training or the knowledge. For a while there's going to be an elite few that will have mastered all these needs.

And then because of the opportunity and the prices, more people will jump in with more processes and more materials. But for the short term, this is a tough area. You know, I took a degree in electrical engineering, but because of the mathematics and field theory, I stayed away from Maxwell's equations. Unfortunately, it's coming that even digital is RF design, and you can't escape.

The only way to escape is to go optical; then you don't have to worry about it at all, because there are no magnetic fields. So, one of the alternatives may be that a lot of 5G may jump into the optical area, simply because of the inherent problems and shortages in the digital electronic area. I think that's what makes it an interesting subject. Going forward, there are an awful lot of challenges.

**Shaughnessy:** Right. It seems like you're just now getting to the point with millimeter wave where they can commercialize it for mainstream. I keep reading about people that have had a hell of a time with millimeter wave, but it seems like they've got it under control now.

**Holden:** UCLA demonstrated for us a millimeter wave chip that had only three connections, and it had replacement mechanical connectors. Because they were so directional that the transmit and receive had to be surface mounted on the edge of the PC board and you didn't need the wire or mechanical connectors because of the millimeter wavelength. A millimeter chip with its own antenna right off the die itself and they're so small you can put quite a few on a wafer. Designing and the architecture of products, they change. The follow up, we're not using mechanical connectors with sockets or anything like that anymore. **Shaughnessy:** John, is there anything you'd like to add?

**Hendricks:** I would just say that everything I've heard has been correct. The millimeter wave does present a lot of challenges, purely from the RF point of view, as has been pointed out. Millimeter wave is nothing new. Not even anything new in consumer applications because you'll see millions of 77-gigahertz radars being produced every year for the automotive industry now, and things like adaptive cruise control. So, from the RF point of view, it's not such a huge challenge. But people are developing new modulation technologies and all kinds of stuff that go with that, which is completely new.

From the PCB side of things, it's the complexity of the boards at those frequencies that's rather new. Even the 77-gigahertz radar is a relatively simple PCB, compared to some of the designs we are starting to see coming along in 5G.

The only other thing that I would point out is when we talk about sub-six gigahertz versus millimeter wave; it's going to be a long time before the millimeter wave really grows that quickly. The initial applications look more like fixed broadband access, and people are working on mobile applications at millimeter wave, so that is a lot more challenging. In the initial, let's say, five-year period, the vast majority of 5G designs are not going to be millimeter wave, at least in terms of production volumes. They're going to be down below six gigahertz.

**Shaughnessy:** Sounds like pretty interesting stuff. It sounds like it's going to make some little disruption, every step of the way. More change.

**Hendricks:** It's the one thing that never changes.

**Shaughnessy:** Well, I appreciate all of you joining us for this talk. I know you're all busy.

Jordan: You too, Andy. Thank you. DESIGN007

## Tech Bends Light More Efficiently, Offers Wider Angles for Light Input

Engineering and physics researchers at North Carolina State University have developed a new technology for steering light that allows for more light input and greater efficiency. At issue are diffraction gratings, which are used to manipulate light in everything from electronic displays to fiber-optic communication technologies.

"Until now, state-of-the-art diffraction gratings configured to steer visible light to large angles have had an angular acceptance range, or bandwidth, of about 20 degrees, meaning that the light source has to be directed into the grating within an arc of 20 degrees," says Michael Escuti, a professor of electrical and computer engineering at NC State and corresponding author of a paper on the work.

"The practical effect of this - in augmented-reality displays, for example - would be that users would have a greater field of view; the experience would be more immersive," says Escuti.

The new grating achieves the advance in angular bandwidth by integrating two layers, which are superimposed in a way that allows their optical responses to work together. One layer contains molecules that are arranged at a "slant" that allows it to capture 20 degrees of angular bandwidth. The second layer is arranged at a different slant, which captures an adjacent 20 degrees of angular bandwidth.

"The next step for this work is to take the advantages of these gratings and make a new generation of augmented-reality hardware," Escuti says.

#### by Andy Shaughnessy I-CONNECTO07

As our consumer electronics reporter, Technology Editor Dan Feinberg has been following 5G for years, since it was a vague idea. For this issue, I asked Dan to give us a breakdown on what 5G is, what it means to our industry, and why moving from 4G to 5G is such a big deal.

**Andy Shaughnessy:** Our current cellular technology is 4G, so why is 5G worrying so many people in the PCB industry and electronics in general? In short, what's the big deal?

**Dan Feinberg:** I'm not sure if it is worrying them, but it will be a challenge for the designers. The big deal is quantum-level improvements in speed, throughput, etc. Some carriers are concerned, however, and that could cause delays. When the carriers upgraded their mobile networks from 3G to 4G some several years ago, it required many billions of dollars in investment in equipment and infrastructure. Initially, the investment did not really yield higher profits. What 4G did eventually was attract new customers, and expand the potential market.

Be aware that voice calls seem to be the best revenue stream for the carriers, and younger callers, who make up the majority of new users, seem to make fewer voice calls. They instead communicate live on iMessage or Whatsapp and a variety of other apps. Also, there is the belief that all things tech should get less costly and the newer generation believes that technology should get cheaper quickly. Therefore, there has to be some concern by the carriers that their vast sums of additional investment might not yield expected returns.

**Shaughnessy:** What are some of the hurdles and questions facing cellular companies who want to launch 5G networks this year?

**Feinberg:** There are lots of questions regarding 5G that will have to be answered, especially in the next year. First of all, what will we use the initial 5G networks for? Will it be cellular or perhaps to replace aging cable or other high-speed data transmission? Another question is

## Candor Circuit Boards

## Innovative solutions for complex circuit board manufacturing

Click to see what we bring to each sector of the industry:

RF/Microwave PCBs

Automotive Electronics

Power Electronics

Lamination

High-Speed Data

Startups

Our technology produces what our customers dream!

### www.candorind.com | (416) 736-6306

where to initially implement, and how quickly the carrier should implement 5G. Remember, there is the issue of speed of implementation vs. cost. One more key question is also economic: Who will become a leader? Who will be one of the first to implement 5G (costly) vs. waiting, and how long should they wait before jumping in. Waiting is less costly, but there is the challenge of catching up. I think that

the hurdles and questions will become more obvious before the year end. As I often say, stay tuned!

**Shaughnessy:** What will 5G mean for PCB laminate suppliers? More high-speed, low-loss materials?

**Feinberg:** 5G will probably require better, improved circuit board laminates and conductors. I am far from an expert on this, but it seems to be obvious to some of the suppliers that the different compo-

nents for high-frequency (and perhaps many varying frequencies) circuits that will be used in a 5G network, including everything from power amplifiers to oscillators, will create new requirements and as-yet unknown issues. 5G may represent the next-gen wireless technology, but it will be a challenge to design and fabricate. I would guess that the circuit board materials used to build circuits that will operate across many different frequencies for 5G will have to undergo changes. However, it is possible that today's high-quality materials will meet some of the need.

**Shaughnessy:** Do you, or anyone, for that matter, know how 5G will affect PCB designers, fabricators, and assembly providers? A lot of people in the PCB world seem to have a waitand-see attitude.

**Feinberg:** I think that the top tier already has a good idea what they will be able to do and

what some of the initial challenges will be. They are more knowledgeable than they probably let on, and it is actually very smart to "wait and see" before going public

**Shaughnessy:** 5G sounds a lot like some of the speeds that our friends in RF and microwave have been dealing with for years. Will they be ahead of the 5G game?

**Feinberg:** I would expect so. Anyone who is used to designing and building high-speed, precision, tighter-spec devices will certainly be ahead of the game.

**Shaughnessy:** You've been covering CES, the Consumer Electronics Show for I-Connect007 for years. What effect do you expect 5G to have on consumer devices such as VR, AR, XR, and autonomous and electric vehicles?

**Feinberg:** It depends. If the XR (cross-reality) is local, such as connected to a local computer or network, with no wireless, 5G will not be a factor. But if it is across the network (Internet) there will be much higher capability, lower lag, and higher resolution. For global XR such as sports events, remote medical treatment, remote military ops, gaming across the net and for greatly improved resolution and response, 5G will be a hugely positive factor, in my opinion. I strongly feel that humanity has entered the "If you can imagine it, it can be done" era, and 5G will be a big enabler to making this happen.

**Shaughnessy:** Thanks for the insight, Dan.

Feinberg: Thank you, Andy. DESIGN007

Dan Feinberg

#### **High Performance Made Simple**

#### The Easy, Powerful, Modern PCB Design Solution

#### AVAILABLE NOW

For more information please visit: www.altium.com/altium-designer

#### by Chang Fei Yee KEYSIGHT TECHNOLOGIES

This article briefly introduces the 4-level pulse amplitude modulation (PAM-4) and its application in 400 Gigabit Ethernet (400GbE), to support the booming data traffic volume in conjunction with the deployment of 5G mobile communications. Furthermore, this article also highlights the essential pre-layout effort from signal integrity perspective for physical (PHY) link design on printed circuit board (PCB), including material selection, transmission line design and channel simulation to support 56Gbps data rate that paves the way for seamless communication in 400GbE.

#### Introduction

400GbE is a new wired communication standard to accommodate the booming data traffic volume with the implementation of 5G mobile communications <sup>[1]</sup>. In the implementation of 400GbE communication, electrical interface with 4-level pulse amplitude modula-

tion (PAM-4) signaling over 8 lanes is adopted. The communication of eight lanes at 56Gbps (i.e., 28GBaud) per lane enables the total bandwidth of 400Gbps over the ethernet. The electrical specifications of 400GbE with PAM-4 signaling are defined in IEEE 802.3bs <sup>[2]</sup>.

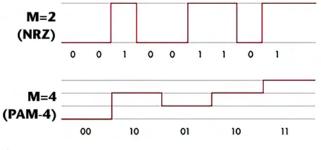

PAM-4 has 4 digital amplitude levels, as shown in Figure 1<sup>[3]</sup>. It has an advantage over non-return-to-zero (NRZ) signals because each level or symbol in PAM-4 contains two information bits providing twice as much data throughput for the same baud rate. For instance, 28GBaud is equivalent to 56Gbps in PAM-4 and 28Gbps in NRZ respectively <sup>[3] [4]</sup>.

## Don't Let Your Temperatures Rise

#### Let ROGERS' Thermal Management Solutions Keep You Cool

COOLSPAN<sup>®</sup> TECA Film • 92ML<sup>™</sup> StaCool<sup>™</sup> Laminates • ML Series<sup>™</sup> Laminates & Prepregs

Heat can be damaging, especially when it is not managed. That's why Rogers Corporation invested so much time and energy into creating an array of material-based thermal management solutions to keep heat rise to a minimum in printed circuits. From automotive circuits to LED modules to power supplies, ML Series laminates and prepregs effectively conduct heat away from the source, while COOLSPAN thermally & electrically conductive adhesive (TECA) materials enhance the thermal management of new and existing designs. And for that extra cooling edge, 92ML StaCool laminates feature a thermally conductive metal bottom plate to enhance the heat dissipation.

| Product | Thickness | Thermal<br>Conductivity | Thermal<br>Impedance, | Tg, C | CTE (Z-Axis),<br>ppm/C                                                   |     | Dk,<br>1MHz | Df,<br>1MHz | Breakdown<br>Voltage, | Flammability |

|---------|-----------|-------------------------|-----------------------|-------|--------------------------------------------------------------------------|-----|-------------|-------------|-----------------------|--------------|

|         |           | (Z-Axis), W/mK          | C-cm2/W               |       | <tg< th=""><th>&gt;Tg</th><th></th><th></th><th>kVAC</th><th></th></tg<> | >Tg |             |             | kVAC                  |              |

| 92ML    | 8mils     | 2.0                     | 0.52                  | 160   | 22                                                                       | 175 | 5.2         | 0.013       | >50                   | HF V-0       |

Advanced Connectivity Solutions

#### www.rogerscorp.com/acs

USA - AZ, tel. +1 480-961-1382 EUROPE - BELGIUM, tel. +32 9 235 3611

Don't let your temperatures rise. Use Rogers' thermal management solutions.

## Essential pre-layout effort from signal integrity perspective

According to guidelines, a PAM-4 channel with trace length up to 8 inches on a PCB shall have insertion loss less than 10dB at 14GHz (i.e., Nyquist frequency of 28GBaud) and 20dB at 28GHz (i.e., 2<sup>nd</sup> harmonic of 28GBaud) respectively <sup>[2]</sup> to achieve seamless data communication between the transceivers. Eight essential pre-layout efforts from signal integrity perspective to be discussed in the following:

#### A. Substrate material selection

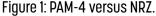

There are three types of PCB substrate dielectric materials categorized based on the dielectric property (e.g., loss tangent and dielectric constant). As seen in Table 1, high-loss materials (e.g., Nelco N4000-6) have a loss tangent above 0.02 and dielectric constant above 4; medium-loss material (e.g., Isola FR408) has a loss tangent of about 0.01 and dielectric constant between 3 and 4. Meanwhile, low-loss materials (e.g., Isola I-Tera MT40) have a loss tangent of about 0.003 and dielectric constant 3.45 <sup>[5]</sup>. Dielectric attenuation is directly proportional to the loss tangent and square root of dielectric constant, as shown in Equation 1 <sup>[6]</sup>.

(Equation 1)

Dielectic attenuation = 0.91 \* f \* loss tangent \*  $\sqrt{\varepsilon_r}$  dB/cm

$\varepsilon_{r}$  = dielectric constant

f = frequency in GHz

Simulated plot of differential insertion loss for dielectric loss effect of 8-inch differential

| Materials       | Dielectric constant | Loss<br>tangent | Example              |

|-----------------|---------------------|-----------------|----------------------|

| High-loss       | 4.3                 | 0.023           | Nelco<br>N4000-6     |

| Medium-<br>loss | 3.6                 | 0.01            | Isola<br>FR408       |

| Low-loss        | 3.45                | 0.003           | Isola I-Tera<br>MT40 |

Table 1: Categories of dielectric materials.

Figure 2: Simulated plot of differential insertion loss for dielectric loss effect with Hyperlynx.

microstrip signals in Figure 2 quantifies the dielectric attenuation for high, medium and low loss materials as 10dB, 5.5dB and 3.5dB respectively at 14GHz. Referring to the guide-line mentioned earlier (i.e., insertion loss less than 10dB at 14GHz for trace length up to 8 inches), low loss material shall be selected to allow more headroom contributed by other channel losses.

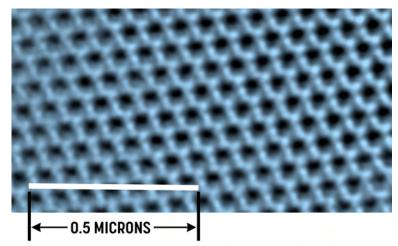

#### B. Fiber weaving

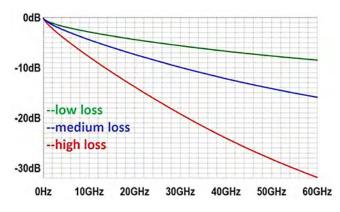

PCB dielectric substrate is composed of woven fiber-glass bound together with epoxy resin. The microscopic top view of PCB substrates of fiber weave styles 1080 and 3313 are illustrated in Figure 3<sup>[7]</sup>. A higher number of fiber glass style (e.g., 3313), refers to denser fiber glass weaving.

Fiber glass material has dielectric properties that differ very much from the properties of epoxy resin. For instance, NE-glass fiber has dielectric constant (Dk) and loss tangent (Df) 4.4 and 0.0006 respectively <sup>[8]</sup>. Meanwhile epoxy resin has Dk 3.2 <sup>[8]</sup>, which is lower than

Figure 3: Fiber weave with glass style 1080 versus 3313.

fiber glass. When a substrate of sparse fiber weaving is used, PCB traces could cross different regions of resin and fiber glass more frequently. As a result, the speed or propagation delay of the signal changes frequently along the trace from transmitting to receiving end. The relationship between them is governed by Equation 2<sup>[9]</sup>.

$$v = \frac{c}{\sqrt{D_k}}$$

Where:

v = signal's speed on PCB (in unit inch/ns) c = speed of light (~12 inches/ns) D<sub>v</sub> = dielectric constant

This scenario poses a great challenge to multi-gigabit differential signals. The homogeneous substrate is the most desired ideal condition, where substrate segment of noninverting signal has the same dielectric properties as inverting signal. However, practically, depending on the fiber weave density, nonhomogeneous substrate condition (i.e., when non-inverting signal is routed on fiber glass, while inverting signal crosses resin region or vice versa) is encountered. Due to the changing propagation delay experienced by the inverting signal, the phase difference between non-inverting and inverting signals in common mode could be much less than 180 degrees at the receiving end. The large extent of skew or misalignment between the rising and falling edges leads to the reduction of width and height of the eye diagram, equivalent to larger differential insertion loss. Ultimately, high bit error is experienced.

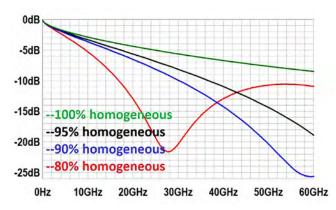

Figure 4 depicts the simulated plot of differential insertion loss for fiber weave effect on differential microstrip signals 8 inches in length. When the non-homogeneous substrate segment increases from 5% to 20% of total channel length, the channel attenuation is increased in the range of 0.7dB and 4dB versus 100% homogeneous at 14GHz. Hence, substrate with denser fiber weave such as 3313 shall be used.

Figure 4: Simulated plot of differential insertion loss for fiber weave effect with Hyperlynx.

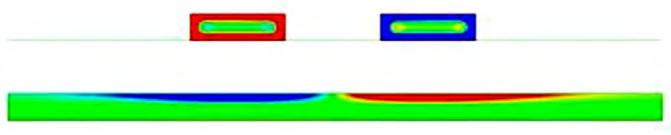

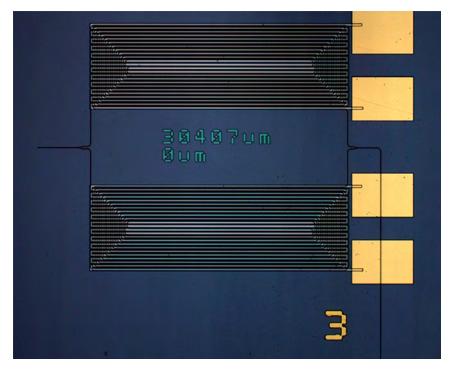

#### C. Copper surface roughness

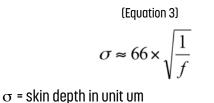

Surface roughness of the copper for trace routing promotes its adhesion to the substrate during PCB fabrication. However, it is necessary to keep the roughness magnitude small. This is because the current of the signal tends to propagate more closely to the surface of the copper trace when the frequency of the signal gets higher. Skin depth is the parameter that determines how extensive the current of signal travels with reference to the surface of the transmission channel. The relationship between skin depth and the signal frequency is governed by Equation 3<sup>[10]</sup>.

f = frequency of signal in unit MHz

There are mainly two types of copper foil used for PCB fabrication, namely rolled copper and electrodeposited (ED) copper. Each type of copper foil has many variations that come with different typical surface roughness. For example, rolled annealed copper has roughness 0.3 um while high profile ED copper has roughness 2.2 um <sup>[11]</sup>. At a given skin depth, a larger magnitude of roughness causes more resistance to the signal propagation.

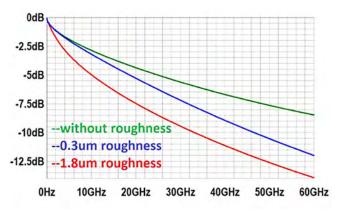

Figure 5 depicts the simulated plot of differential insertion loss for conductor surface

Figure 5: Simulated plot of differential insertion loss for copper surface roughness effect with Hyperlynx.

roughness effect on a microstrip channel eight inches in length. At 14GHz, 0.3um roughness introduces an additional 0.5dB, while 1.8 um roughness adding an extra 2.5dB attenuation versus a totally smooth copper surface. Hence, hardware developer shall choose the PCB fab houses that offer copper foil type with surface roughness 0.3 um or less to mitigate the attenuation and distortion of the signal transmission.

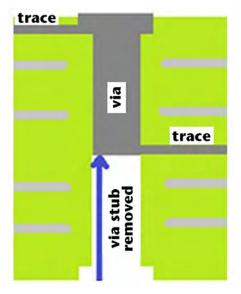

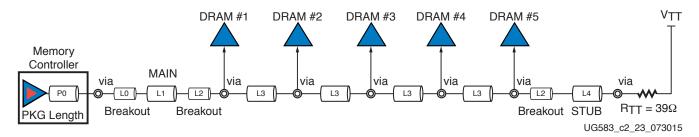

#### D. Minimizing via stub

Blind or back-drilled vias (Figure 6) shall be applied for IC pin break out on PCB to minimize the stub length, which in turn pushes the quarter wave resonant frequency higher, thereby increasing the bandwidth of the physical channel. With reference to Equa-

Figure 6: Blind or back-drilled via.

tion 4 <sup>[12]</sup>, the quarter wave resonant frequency is inversely proportional to the stub length. Rearranging Equations 4 and 5 <sup>[13]</sup>, for 56Gbps (i.e., 28GBaud) PAM-4 transmission on PCB with low-loss material, where Dkeff is 3.45, the maximum stub length would be ~ 11 mils.

$f_o > 2 \ge 2 \ge 5 \ge 100$  x 2.5 x baud rate

Where:

f<sub>a</sub> = quarter wave resonant frequency (Hz)

c = speed of light (~12 inches/nano-second) stub\_length in inches

D<sub>koff</sub> = effective dielectric constant

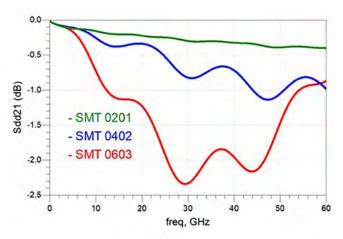

### E. Minimizing impedance mismatch due to mounting pad of AC coupling capacitor

The mounting pad of the AC coupling capacitor has wider copper versus the PCB trace. For example, the capacitor in a 0201 package has 10 mil pad width, while 0603 package has 30 mil pad width <sup>[14]</sup>, while PCB microstrip trace width is normally set not more than 10 mils. Referring to Equation 6 and 7 respectively <sup>[15]</sup>, a wider copper in mounting pad versus PCB trace increases the capacitance, which in turn causes capacitive discontinuity or mismatch to the characteristic impedance of the transmission line in single ended mode.

Figure 7 depicts the simulated plots of differential insertion loss for microstrip traces (i.e., 500 mil long and 6 mil wide in singleended mode) interface with capacitor in 0201, 0402 and 0603 package respectively. A wider mounting pad contributes to a larger impedance discontinuity, which in turn causes a larger insertion loss due to more severe signal reflection. The attenuation at 14GHz due to 0603 (i.e., 1.2dB) and 0402 (i.e., 0.4dB) packages are at least double of 0201 (i.e., 0.2dB). Hence, designers should use capacitors in a

Worldwide Provider of Flexible Circuits & Printed Circuit Boards

### **Unwavering Commitment**

We put the customer first by listening to their needs, allowing our team to maximize accuracy and consistently deliver high quality products.

With our on time delivery record of 94.96%, you can expect your product to be delivered on time and to your standards, making us the best choice in the industry. **Contact us** today for a consultation.

tramontocircuits.com

info@tramontocircuits.com

1.877.777.1977

smaller package, e.g., 0201 (i.e., 10 mil pad width) to minimize the discontinuity.

(Equation 6)

$$Z_o = 31.6 \times \sqrt{\frac{L_o}{C_o}}$$

Where:

- L<sub>o</sub>= intrinsic loop inductance per unit length of the transmission line (in nH/cm)

- C<sub>0</sub>= intrinsic capacitance per unit length of the transmission line (in pF/cm)

- Z<sub>o</sub> = characteristic impedance (in ohm)

(Equation 7)

$$C = \frac{\varepsilon_r \varepsilon_o wl}{d}$$

Where:

- C = capacitance (in pF)

- $\epsilon_r$  = relative permittivity of substrate

- $\varepsilon_0^{1}$  = permittivity of vacuum

- w = width of SMT pad (in cm)

- I = length of SMT pad (in cm)

- d = distance between mounting pad and reference plane underneath (in cm)

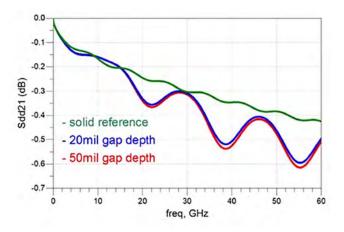

#### F. Providing continuous reference plane

When the PCB trace crosses over a gap between 2 split planes, an inductive impedance discontinuity or non-continuous refer-

Figure 7: Differential insertion loss for varying surface mount pad width in series with 500 mil long PCB trace, simulated in Keysight EMPro. ence is encountered. This phenomenon is governed by Equations 6 and 8 <sup>[15]</sup> respectively. When the gap between split planes is crossed over, the distance between the trace and reference underneath (i.e., gap depth) is increased, this leads to the rise of inductance, which in turn causes the trace impedance to increase over the split. With reference to simulated plots of differential insertion loss in Figure 8, where crossing over split planes results in higher insertion loss due to larger inductive impedance discontinuity, with minimum 0.1dB attenuation at 20GHz and beyond.

(Equation 8)

$$L \approx 2x [\ln(\frac{5.98d}{0.8w+t})]$$

Where:

- L = parasitic inductance of copper trace (in nH)

- d = distance between copper trace and reference underneath (cm)

- w = width of copper trace (cm)

- t = thickness of copper trace (cm)

- x = length of copper trace (cm)

In addition to that, non-continuous reference plane or return path also creates larger loop areas that increase mutual inductance and signal crosstalk <sup>[16]</sup>. Hence, it is essential to ensure a solid reference plane along the entire trace length path.

Figure 8: Differential insertion loss for 500 mil PCB trace with solid reference versus crossing over split planes simulated in Keysight EMPro.

#### G. Minimizing signal crosstalk

Crosstalk causes noise induction in victim signals which in turn increases the bit error at receiving IC. Therefore, in addition to providing continuous reference plane mentioned above, non-interleaved routing shall also be applied on stripline, due to a lower far end crosstalk (FEXT) compared to near end crosstalk (NEXT). Whereas interleaved routing be applied on microstrip due to a lower NEXT compared to FEXT. Channel analysis <sup>[17]</sup> compares the NEXT versus FEXT on microstrip and stripline respectively in time domain. Besides that, inter-pair spacing shall be at least triple the trace width <sup>[18]</sup>.

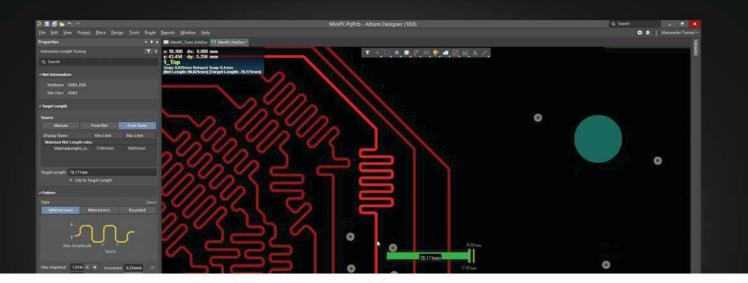

#### H. Intra-pair skew

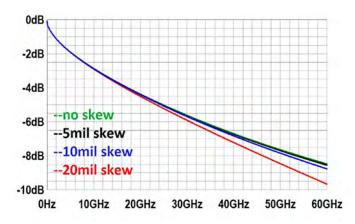

Intra-pair skew in PCB traces introduces higher insertion loss, which in turn increases the bit error of the physical channel, due to the fact that when inverting and non-inverting signals are not 180 degrees out of phase, the eye height in differential mode becomes smaller. The impact of intra-pair skew on signal integrity is shown in differential insertion loss plots in Figure 9, where larger skew leads to higher insertion loss. Therefore, each physical channel's intra-pair skew shall be kept within 5mil to mitigate the transmission loss. The skew

Figure 9: Differential insertion loss plots for eight-inch PCB trace with varying intra-pair skew simulated in Hyperlynx.

can be minimized using serpentine routing technique <sup>[19]</sup>. However, the differential impedance changes once the intra-pair spacing is increased in serpentine segment. Hence, intrapair spacing for serpentine and non-serpentine segments shall not differ too much, to minimize the full path differential impedance tolerance or discontinuity within  $\pm 5\%$ .

#### **PAM-4 channel simulation**

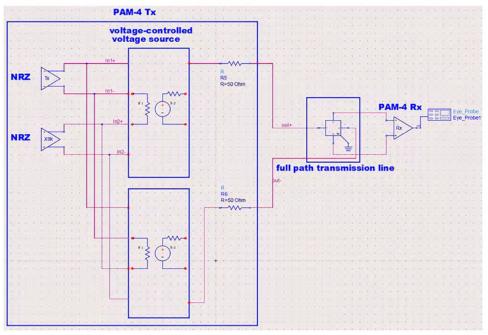

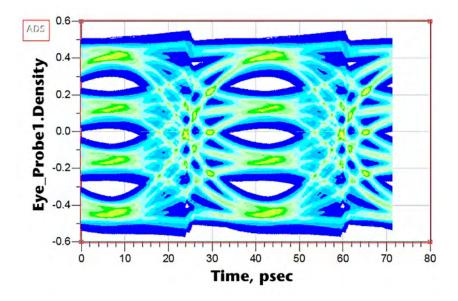

Figure 10 depicts the channel simulation topology using Keysight ADS at BER 1e-6, where

Figure 10: PAM-4 channel simulation topology at 28GBaud using Keysight ADS.

Figure 11: Eye diagram at receiver resulted from channel simulation topology in Figure 10.

two NRZ signals at 28GBaud are injected to voltage-controlled voltage source to generate a PAM-4 signal at 56Gbps. Simulation models of PCB traces, break out vias, transmitter IC package and receiver IC package are lumped in the full path transmission line. At the transmitting end, the signal amplitude and rise/fall time are 1.2Vpp and 16ps respectively. The PAM-4 eye diagram in Figure 11 has three eyes due to its four digital amplitude levels. Decision feedback equalization (DFE) at receiver is enabled. The channel simulation yields 90mV eve height and 15ps eve width. The results have to meet the specification in <sup>[20]</sup> before PCB prototyping for actual physical layer compliance test in <sup>[21]</sup>.

#### Conclusion

All the essential pre-layout effort discussed in this article should be taken seriously in designing PAM-4 PHY channels on PCB, including material selection, transmission line design and channel simulation. It is important to implement the 56Gbps PAM-4 PHY link in a stringent manner to guarantee a robust and seamless communication between the highspeed transceivers, paving the way for reliable 400GbE. **DESIGN007**

#### References

The 2015 Ethernet Roadmap.

Baseline Proposal for CDAUI-8 Chip-to-Module (c2m).

3. W. Wong, What's the Difference Between NRZ and PAM.

4. Keysight Technologies: PAM-4 Design Challenges and the Implications on Test.

5. Isola I-Tera MT40 data sheet.

6. Transmission Line Loss.

7. PCB Material Selection for High-speed Digital Designs.

**8**. PCB Dielectric Material Selection and Fiber Weave Effect on High-Speed Channel Routing.

9. E. Bogatin, Signal Integrity—Simplified (1st Edition).

10. B. Olney, Effects of Surface Roughness on High-speed PCBs.

11. J. Coonrod, Choosing Cop-

per Foils for High Frequency PCBs.

12. E. Bogatin, L. Simonovich, S. Gupta, M. Resso, Practical Analysis of Backplane Vias.

13. E. Bogatin, How long a stub is too long: Rule of Thumb #18.

14. Size Chart - Footprint Selection.

15. High-Speed Analog Design and Application.

16. B. Olney, Return Path Discontinuities.

17. L. Simonovich, Guard Traces.

18. L. Simonovich, Crosstalk.

19. High-Speed Interface Layout Guidelines.

20. 802.3bs-2017 - IEEE Standard for Ethernet—Amendment 10: Media Access Control Parameters, Physical Layers, and Management Parameters for 200 Gb/s and 400 Gb/s Operation.

21. Keysight Technologies, How to overcome test challenges in 400G/PAM-4 designs.

**Chang Fei Yee** is a hardware engineer with Keysight Technologies. His responsibilities include embedded system hardware development, and signal and power integrity analysis.

#### ITI & IPC Conference on Emerging & Critical Environmental Product Requirements

June 4 • BOSTON, Massachusetts June 6 • CHICAGO AREA, Illinois June 8 • SILICON VALLEY, California

It is a continuing challenge to stay current on global environmental regulations and issues such as:

- The EU Circular Economy Strategy

- EU RoHS exemptions

- REACH regulation registration and enforcement

- China and Southeast Asia environmental restrictions

- The Toxic Substances Control Act (TSCA)

- California Green Chemistry Initiative

That is why IPC and ITI are again joining forces to help keep you ahead of the curve and connect you with leading industry speakers, update you on the latest trends and offer networking opportunities at the <u>2018 Emerging & Critical Environmental</u> <u>Product Requirements Conference</u>.

This conference will provide anyone who is responsible for keeping their organization in compliance with environmental regulations the tools they need to comply with legal, regulatory, and customer requirements.

**<u>Register today</u>** and stay ahead of the curve on the changing state of global environmental regulations!

For more information, contact **Ken Schramko**, IPC director of government relations, at **KenSchramko@ipc.org**.

## Making the Most of PCB Materials for 5G Microwave and mmWave Amps

#### by John Coonrod Rogers Corporation

Millions of cellphones trying to connect voices and download unimaginable numbers of files worldwide point to the inevitability of fifth generation (5G) wireless communications networks. 5G is coming, and it will require the right circuit materials for many different types of high-frequency circuits, including power amplifiers (PAs). 5G represents the latest and greatest in wireless technology, and it will be challenging to design and fabricate, starting with the circuit board materials, because it will operate across many different frequencies, such as 6 GHz and below, as well as at millimeter-wave frequencies (typically 30 GHz and above). It will also combine network access from terrestrial base stations and orbiting satellites. But by careful consideration of mechanical and electrical requirements, high-frequency circuit materials can be specified that enable the design and development of 5G PAs no matter the frequency.

Ideally, a single circuit material would be a suitable starting point for PAs at all frequencies. However, amplifiers at different frequencies have different design requirements and are best supported by circuit materials with different characteristics best suited to the different frequencies. For example, insertion loss or dissipation factor can be more or less depending on the type of circuit material. Every circuit material will suffer some amount of loss, which typically increases with increasing frequency. The loss performance of a given circuit material may be acceptable within the microwave frequencies to be used in 5G networks but not within the millimeter-wave frequency range, where signal power tends to be less with increasing frequencies. The circuit material that provides the low loss needed for high PA gain and output power at microwave frequencies may not be the best choice of material for a PA at millimeter-wave frequencies.

The design requirements for a key circuit material parameter, dielectric constant (Dk), are much different for microwave frequencies,

## Offshore pricing. Exceptional quality. Local service.

We strive for excellence in everything we say and do.

Our finger is on the pulse of the latest technologies, systems and solutions in an effort to be a total PCB solution provider for our customers.

#### Why choose Eagle as your total PCB provider:

- . Dedicated offshore team with local quality and engineering support

- Seamless transition from prototype to production

- . The same exceptional service and support that you've come to expect from Eagle

Click here to learn more about our offshore option

such as the 6 GHz and below used with 5G systems, than for millimeter-wave frequencies, such as 30 GHz and above, as will be used for short-range backhaul links in 5G wireless networks. Selecting an optimum circuit material for each band of frequencies requires understanding which Dk value best supports each of the two different frequency ranges. Then it is a matter of finding circuit materials that possess those Dk values along with as many as possible of the other circuit material attributes that help make a good, high-performance, high-frequency PA.

### Selecting an optimum circuit material for each band of frequencies requires understanding which Dk value best supports each of the two different frequency ranges.

Whether for microwave or millimeter-wave frequencies, circuit materials for high-frequency PAs must be capable of supporting circuitry that achieves the impedance match to the power transistors in those PAs. Such impedance matching is also necessary for the active devices in lower-power amplifiers, such as driver amplifiers and even in low-noise amplifiers (LNAs).

Suitable circuit materials for such impedance-matching networks must be capable of keeping circuit impedance variations to a minimum, and this is typically done through tight control of the substrate thickness, with no variations in thickness; tight control of conductor widths, such as microstrip transmission lines, to maintain the same impedance; tight control of the copper thickness on circuit laminates; and tight control of the circuit material's Dk, especially with temperature. Although using a circuit material with tight control of Dk, such as  $3.50 \pm 0.05$ , can help maintain the impedance of high-frequency transmission lines within a narrow window as might be needed for impedance matching within a PA circuitry, variations in the substrate thickness can have even more impact on maintaining consistent impedance of high-frequency transmission lines. A circuit material with a Dk tolerance of  $\pm 0.05$  or lower is considered to have a tightly controlled Dk value.

With increasing frequencies, signal wavelengths are decreasing, requiring ever-smaller circuit features. Many of the PA circuit configurations used at both microwave and millimeterwave frequencies, such as Doherty amplifiers, are dependent upon quarter-wavelength transmission-line circuit structures and the dimensions of these structures are a function of the substrate thickness. If that circuit substrate thickness is not tightly controlled, it is easy to understand how the impedance of extremely fine transmission-line and circuit structures can vary with those variations in substrate thickness. In general, a substrate thickness variation of  $\pm 10\%$  or better is a sign of tightly controlled circuit material thickness.

#### **Feeling the Heat**

Whether at microwave or at millimeter-wave frequencies, PA circuits are subject to performance variations brought about by changes in temperature, from both the operating environment and from the PA's own active devices, such as power transistors or ICs. In the search for circuit materials for both microwave and millimeter-wave PAs for 5G applications, finding circuit materials capable of effective thermal management is critical to minimizing a PA's performance variations as a result of the thermal rise brought about by its own active devices. Two circuit material parameters are of particular interest when assessing a material's thermal behavior: thermal conductivity and thermal coefficient of dielectric constant (TCDk).

High thermal conductivity allows for efficient flow of heat away from any heat-generating active devices mounted on a PCB, such as a PA's power transistors. Consistent heat flow not only removes the heat as a threat to the reliability of the transistors, but helps minimize thermally inducted PA performance variations. Thermal conductivity of 0.5 W/mK or higher is considered good for a PCB material.

TCDk is a circuit material parameter that indicates how that material's Dk is affected by variations in temperature. Ideally, a material would have a TCDk of 0 ppm/°C for no change in Dk with temperature. But practical circuit materials exhibit some changes in Dk with temperature and a TCDk of 50 ppm/°C is considered good for a circuit material, resulting in only small changes in Dk with temperature. For the amplifiers and other circuits in 5G systems that will rely on fine quarter-wavelength circuit structures, circuit materials with low TCDk values will help minimize performance variations.

The smaller wavelengths and circuit features needed for millimeter-wave PAs and circuits in general will require thinner substrate materials compared to lower-frequency microwave PAs and circuits, and maintaining a tight tolerance in that thickness is just as critical as for thicker materials. Those thinner circuit materials can also be more sensitive than thicker circuit materials to the effects of other circuit material characteristics, such as copper surface roughness. Copper surface roughness can result in such circuit effects as transmission-line loss and phase variations, so copper surface roughness should be minimized in any circuit materials specified for the smaller-wavelength, higherfrequency circuits in both 5G microwave and millimeter-wave PAs.

As an example, Rogers offers a variety of materials with different thicknesses and other characteristics needed for the two different frequency ranges. For 5G PAs at 6 GHz and below, 20- and 30-mil-thick ceramic-based RO4385 circuit laminates are low-cost circuit materials that maintain consistent performance across wide temperature ranges. They have a Dk of 3.48 in the z-axis at 10 GHz, tightly controlled within  $\pm 0.05$ . They are ideal for competitive applications and can be fabricated with standard epoxy/glass (FR-4) processes.

For 5G PAs at millimeter-wave frequencies, 5- and 10-mil-thick RO3003 laminates consist of PTFE with ceramic filler. They feature a Dk of 3.0 in the z-axis at 10 GHz tightly controlled within  $\pm$  0.04. They feature extremely low loss at higher frequencies that helps get the most gain from the active devices in an amplifier circuit, even at the various millimeter-wave bands expected to serve the many backhaul links of future 5G wireless networks. **DESIGN007**

This article originally appeared in February 2018 as a blog in Microwave Journal.

John Coonrod is technical marketing manager for Rogers Corporation.

### **Design for Magnetoelectric Device May Improve Your Memory**

For years, manufacturers have offered computers with increasing amounts of memory packed into smaller devices. But semiconductor companies can't reduce the size of memory components as quickly as they used to, and current designs are not energy-efficient. One promising version of magnetic device relies on the magnetoelectric effect. Existing devices, however, tend to require large magnetic and electric fields that are difficult to produce and contain.

One potential solution for this problem is a new switch-

ing element made from chromia (Cr2O3), which, one day, may be used in computer memory and flash drives. "The device has better potential for scaling, so it could be made smaller, and would use less energy once it's suitably refined," said Randall Victora, a researcher at the University of Minnesota and an author on the paper.

Next, Victora and Ahmed aim to collaborate with colleagues who work with chromia to build and test the device. If successfully fabricated, then the new device could potentially replace dynamic RAM in computers.

#### All About Flex: ISO 9001 Basics 🕨

ISO 9001 is an internationally recognized standard that specifies requirements for a business's or organization's quality management system. Companies achieving ISO 9001 certification are audited to review compliance for systems to assure products or services are delivered with a consistent quality level and meet agreed upon specifications.

## It's Only Common Sense: Taming the Extraordinary Salesperson >

We spend a great deal of time talking about how to handle poor-performing salespeople those who are not making their numbers, or those who just can't seem to get out there and visit customers, get an appointment, or close a sale.

## IPC 6012-DA Revisions: The Approach to Cleanliness, Thickness, Inspection, and Wicking ►

IPC's Automotive Addendum task group was started in November 2014 and the first edition of IPC 6012-DA was released in April 2016. We are now working on the revised version and expect a release in Q2 2018. As standards need to evolve, develop and follow the needs of the industry, this work is continuous.

## PCB Manufacturing (R)evolution in the Making >

At the recent HKPCA and IPC Show 2017 in Shenzhen, China, I was able to interview Les Sainsbury, CEO, and Andrew Kelley, CTO, of XACT PCB, as well as Alex Stepinski, vice president of Whelen Engineering's PCB Fab Business Unit, to discuss process evolution and technology developments in the PCB manufacturing industry.

## Flex to Divest Multek's China Operations to MFLEX >

Flex Ltd. has entered into an agreement with Multi-Fineline Electronix Inc. (MFLEX), a wholly-owned subsidiary of Suzhou Dongshan Precision Manufacturing Co., Ltd (DSBJ), to divest the China-based operations of the Flex subsidiary, Multek.

#### Weiner's World–March 2018 🕨

SEMICON China 2018 was amazing in its size and attendance. More than 1,000 exhibitors filled an event venue of more than 74,000 square meters of exhibition space—the size of nearly 10 professional soccer fields. This year's theme was "collect, collaborate, innovate."

## Aspocomp Acquires Technopolis Facility in Finland

Aspocomp Group Plc has acquired the production facility from Technopolis Plc, located in the Linnanmaa district in Oulu, Finland.

## IPC APEX EXPO 2018..the Show Goes On! >

Access I-Connect007's first edition of *Show & Tell Magazine* as a flip book! Inside you will find exclusive interviews, photos, videos, contest results, and commentary that will show and tell you all about this year's event.

## It's Only Common Sense: The Cost of Keeping a Customer >

Experts estimate that we spend hundreds, if not thousands of dollars acquiring new customers each year. When you think of all the money we spend on marketing, advertising, trade shows, websites, salespeople, and their travel and other expenses, you know these experts are right.

# Test Drive OrCAD

### Transform Your Ideas Into Reality

Experience the benefits of fast, accurate printed circuit board design and analysis with the OrCAD<sup>®</sup> free trial. Your dreams can shape the future; OrCAD can help you make them a reality.

Get The Free Trial >

## Common Symptoms of Common-Mode Radiation

### **Beyond Design**

by Barry Oiney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

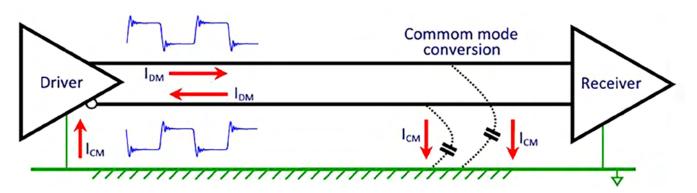

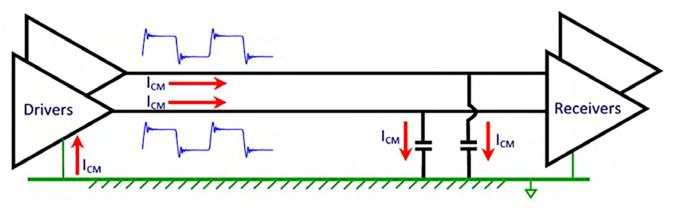

Electromagnetic radiation from digital circuits, can occur as either differential mode or common mode. Differential mode is typically equal and opposite and therefore any radi-

ating fields will cancel. Conversely, common-mode radiation from two coupled conductors is identical. It does not cancel but rather reinforces.

Unfortunately, differentialmode propagation can be converted to common mode by parasitic capacitance or any imbalance caused by signal skew, rise/fall time mismatch or asymmetry in the

channel. Also, return path discontinuities can create large common mode loop areas that increase series inductance and electromagnetic radiation. In this month's column, I will explore the common symptoms of, and present some cures for, common mode radiation.

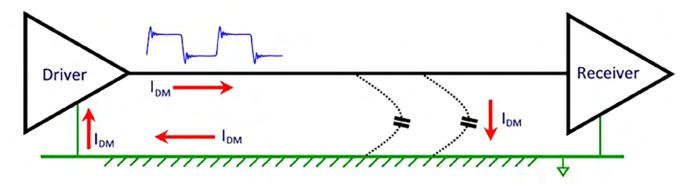

Differential mode radiation accompanies normal circuit operation and is the result of current flowing in the return path loop formed by the PCB conductors (traces and reference planes, as in Figure 1). Microstrip (outer layer) loops can act as small antennae that predominately radiate magnetic fields, whereas stripline (inner layer) loops only emit radiation from the fringing fields at the edge of the PCB. Although these signal loops are necessary for circuit operation, their size and loop area must be controlled during the design process to minimize radiation.

> Fortunately, it is not necessary to evaluate each loop individually. However, the most critical loops should be

analyzed. The other loops can be controlled by good stackup design practices. Please refer to the structural guidelines in my *Beyond Design: Stackup Planning Parts 1-4* columns <sup>[1]</sup> for further information.

Generally, the most critical loops are the highest frequency where the signal is periodic. In a synchronous circuit, the clock is a sequence of repetitive pulses that generates the most emis-

Figure 1: Normal (differential mode) signal return current.

# We Look Deep Into Every Project Design For Manufacturability Expertise is Critical

### A Leading Manufacturer of High Reliability Printed Circuit Boards

The core competency that drives APCT is detailed engineering support enabling superior execution. To that end, our highly qualified DFM staff goes into great depth when reviewing the design & feasibility of each new project. If we can save our customer a reiteration or two, we can save a significant amount of time & money. This philosophy creates a quiet confidence and from that confidence emerges trust. Let the DFM team at APCT look deep into your project and insure the trust of a quality build.

### APCT, "Where Our People Differentiate Us From The Competition"

|             | APCT                                                                                                                                                                                                                                    | Offers                          |                                                                                                                                                                             |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TECHNOLOGY  | Standard:2 - 28LayersAdvanced:30 - 38LayersDevelopment:40 plusLayersLam Cycles:7x7xMicro BGA Pitch:.2MillimetersFlex/Rigid Flex:2 - 30Layers                                                                                            | CERTIFICATIONS                  | AS9100D Certified<br>NADCAP Certified<br>MIL-P-55110 Certified<br>MIL-PRF-31032 (Pending Approval)<br>IPC 6012 Class III                                                    |  |  |

| CYCLE TIMES | <ul> <li>Through Hole Technology</li> <li>2 - 10 Layers, 24 Hours</li> <li>2 - 24 Layers, 48 Hours</li> <li>HDI Technology</li> <li>Via in Pad: 48 - 72 Hours</li> <li>HDI: 3 - 15 Days*<br/>*Depending upon # of lam cycles</li> </ul> | QUANTITIES                      | ITAR Registered at all sites<br>From Prototypes to full scale<br>Production orders with off-shore<br>Solutions through APCT Global<br>No Tooling Charges<br>No Test Charges |  |  |

| APCT.com    | APCT Santa Clara<br>Corporate HQ<br>408.727.6442<br>Corporate HQ<br>ADivision of APCT<br>ADIVISION OF APCT                                                                                                                              | APCT Orange Cou<br>714.993.0270 | APCT Wallingford         APCT Global           203.269.3311         203.284.1215                                                                                            |  |  |

sions. Clock signals should always be routed first, and every effort should be made to route them in the absolute minimum loop area possible. The length of the clock trace should be minimized as well as the number of layer transition vias. On a multilayer PCB, clocks should be routed on a stripline (inner layer) adjacent to a solid reference plane to reduce radiation. The spacing between the clock trace and the return plane should be as small as possible to increase coupling and reduce loop area. Also, to prevent the clocks from coupling to cables, that leave the PCB assembly, the clock circuitry should be located well away from I/O connectors and cables.

Data and address buses, together with their associated command and control signals, are second on the critical list. These buses are normally terminated and can carry large peak currents that radiate proportionally to the current transferred. Transient power supply currents can be another significant source of differential radiation. Although these loops can be quite small, they can carry large currents during switching.

Differential mode radiation is proportional to the frequency squared and can be controlled by reducing the power distribution network (PDN) impedance to below the required target impedance, minimizing the loop area, cancelling out the fields by using differential signals and by dithering the clocks. If the amplitude of the emission is spread out, in the frequency band, then the radiation is also reduced. Spread spectrum clocking can reduce the radiation by up to 15dB.

If a differential pair is well balanced, then tight coupling will achieve an effective degree of field cancellation. However, if they are not perfectly balanced (Figure 2), then the degree of cancellation is not determined by the spacing, but rather by the common mode balance of the differential pair. Most digital drivers have poor common mode balance and therefore differential pairs often radiate far more power in the common mode than in the differential mode. In such a case, one gains no radiation benefit from coupling the differential traces more closely together. Figure 3 highlights the simulated common-mode return current in the reference plane of the cross-section of an imbalanced differential pair.

Differential signals that are closely coupled will operate mainly in the differential mode

Figure 2: Differential-mode signals can be converted to common mode.

Figure 3: Coupled microstrip differential pair (courtesy Ansoft).

Figure 4: Common-mode signal return path.

with some common mode radiation from imbalances in the signals. If the two traces are separated enough to prevent coupling, then both act as single-ended signals. So a 100-ohm differential pair becomes two individual 50-ohm single-ended signals. This is fine, providing the loop area is small and the impedance does not change along the length of the signals.

In contrast, the "bad guy," common-mode radiation, is the result of parasitics in the circuit which emanate from the unwanted voltage drops in the conductors. As the signal is driven down the transmission line, capacitive coupling between the trace and plane conductors completes the loop and displacement current flows through the capacitance which returns to the source (Figure 4). The common-mode current that flows through the ground impedance produces a voltage drop in the digital logic ground system and generates magnetic radiation.