an IConnect007 publication

Working with Circuit Design Engineers p.10

The Roles of the Designer and Design Engineer p.16

Much More!

# **PCB Designers and Design Engineers**

Communication is Key

# **PCB BUYERS**compare nearly 1900 manufacturers now at The PCB List.

**Quick Search**

Advanced Search

The best way to find a PCB fabricator, anywhere.

### www.thepcblist.com

Thursday, May 12th, 2016 3:00pm - 8:00pm Irvine, Calif. Marriott Interested in sponsoring? Contact us here.

Calling all **West Coast Geeks...** this year we have expanded our event to Orange County... **be there because you** *are* **square!**

Check out this short drone video of last year's event in Minneapolis where we hosted over 300 attendees.

Learn more at: tntgroup.org

### Join us May 12th to:

- Network with peers from all aspects of the electronics community

- Enjoy good food and music

- Meet new friends and catch up with old ones (well not *THAT* old!)

- Learn about the latest and greatest products and technology

- Connect with industry suppliers in a relaxing atmosphere

#### We look forward to seeing you!

EXCLUSIVE MEDIA SPONSOR

#### **April 2016**

# **UESION** Feature Content

# Design Engineers and PCB Designers

Some PCB designers say that working with their design engineers is one of their biggest hurdles. Others say it all comes down to a lack of communication. We asked a variety of engineers and designers to discuss the reasons for this divide, and what can be done to address this problem. This month we have feature articles by design instructor Rick Hartley and Analog Home's Steve Hageman, as well as interviews with lead designer Andy Critcher of Total Board Solutions and Randy Faucette, director of engineering at Better Boards Inc.

- **10 Working with Circuit Design Engineers** *by Rick Hartley*

- **16 The Roles of the Designer** and the Design Engineer Interview with Steve Hageman

- 22 Designers and Engineers: Two Sides of the Same Coin Interview with Andy Critcher

- **30 The Partnership: Design Engineers and PCB Designers** *Interview with Randy Faucette*

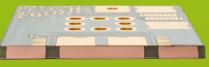

# **185HR** High-Tg, Low-CTE Materials with High Thermal Reliability

#### **FEATURES**

- High Thermal Performance

- Tg: 180°C (DSC) (Base Laminate)

- ▶ Tď: 340°C (TGA @ 5% wt loss)

- Low CTE for reliability

- T260: 60 minutes

- T288: >15 minutes

- · Lead-free Compatible and RoHS Compliant

- UV Blocking and AOI Fluorescence

- High throughput and accuracy during PCB fabrication and assembly

- Superior Processing

Closest to conventional FR-4 processing

- Industry Approvals

- IPC-4101D-WAM1 /98 /99/ 101 /126

- UL File Number E41625

- Qualified to UL's MCIL Program

#### **KEY APPLICATIONS**

- Heavy copper, 6 & 12 oz automotive applications

- Military

- Medical

- Industrial

- · Core Material Standard Availability

- Thickness: 0.002" (0.05 mm) to 0.060"/0.062" (1.5 mm)

- Àvailable in full size sheet or panel form

- Prepreg Standard Availability

- Roll or panel form

- Tooling of prepreg panels available

- · Copper Foil Type Availability

- Standard HTE Grade 3

- RTF (Reverse Treat Foil)

- Copper Weights

- ½, 1 and 2 oz (18, 35 and 70 μm) available

- Heavier copper available upon request

- Thinner copper foil available upon request

#### · Glass Fabric Availability

- Standard E-glass

- Square weave glass fabric available

#### **ORDERING INFORMATION:**

Contact your local sales representative or visit www.isola-group.com for further information.

Isola Group 3100 West Ray Road Suite 301 Chandler, AZ 85226 Phone: 480-893-6527 info@isola-group.com

Isola Asia Pacific (Hong Kong) Ltd.Isola GmbHUnit 3512 - 3522, 35/FIsola StrassNo. 1 Hung To Road, Kwun Tong,<br/>Kowloon, Hong KongD-52348 Dür<br/>Phone: 49-2Phone: 852-2418-1318info-dur@isinfo.hkg@isola-group.comIsola Strass

Isola GmbH Isola Strasse 2 D-52348 Düren, Germany Phone: 49-2421-8080 info-dur@isola-group.com

**April 2016**

Vol. 5, No. 4

thepcbdesignmagazine.com

#### SHORTS

- 14 Hannover Messe: Industry 4.0 Has Become a Reality

- 20 And the Survey Said: What are Your Pain Points?

- 28 University of Sussex Research Brings 'Smart Hands' Closer to Reality

- 34 LOPEC 2016–Printed Electronics: A Key Technology of the Future

- 49 The Automotive Market is Turning Electric

- 60 Survey: Consumers Seeking Higher Value Proposition for Home Internet of Things

- 79 Humanoid Robotics and Computer Avatars

#### DEPARTMENTS

- 82 Events Calendar

- 83 Advertisers Index & Masthead

# **More Content**

#### ARTICLES

- 64 SiSoft: Optimizing the State of the Art Interview with Todd Westerhoff

- 70 Behind the Scenes: Adcom's TLA Award-Winning Design by Ruth Kastner

- 76 The Gerber Guide, Chapters 9 & 10 by Karel Tavernier

#### COLUMNS

8

- **Leaving Las Vegas, on a High Note** by Andy Shaughnessy

- **38 DDR3/4 Fly-by vs. T-topology Routing** *by Barry Olney*

- **46 The Basics of Hybrid Design, Part 2** *by Tim Haag*

- **50 Design Tips for Easier Conformal Coating** *by Phil Kinner*

- 54 Outsourcing PCB Design: How it can Help by Mark Tinkler

- 58 What is Signal Launch and Why Should You Care? by John Coonrod

#### HIGHLIGHTS PCB007

62 MilAero007

36

80 Top Ten PCBDesign007

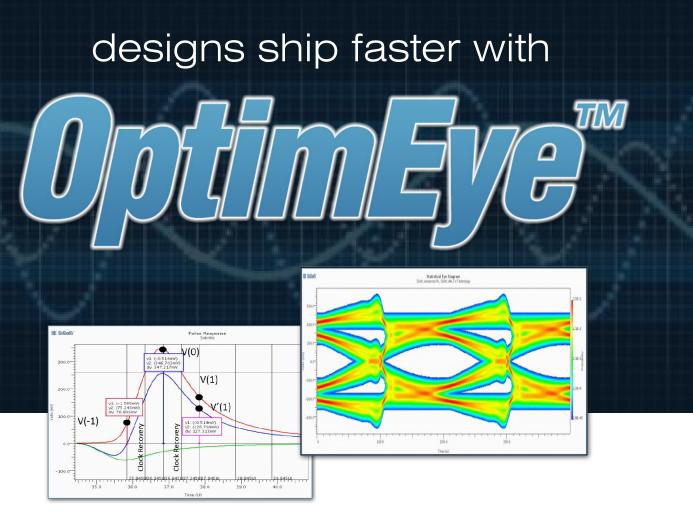

# OptimEye works with existing AMI vendor models to find the ideal balance between Tx and Rx equalization settings up to 100x faster than traditional methods.

SiSoft's new OptimEye technology lets you replace hundreds of blind sweep simulations with a single run that determines the optimal balance of Tx/Rx equalization automatically. Designed specifically for AMI-based analysis, OptimEye runs fast enough to generate custom per-channel equalization settings in a large system design with thousands of serial links.

#### Learn more about OptiEye™

DOWNLOAD OUR WHITEPAPER New SI Techniques for Large System Performance Tuning Presented at DesignCon 2016

www.sisoft.com

# Leaving Las Vegas, on a High Note

#### by Andy Shaughnessy

I-CONNECT007

Every show is different, but IPC APEX EXPO 2016 has to be the best trade show I've ever attended. There was just no downside, at least for I-Connect007.

We covered the show from beginning to end, made a lot of new friends, and basically "spread the love," as I like to say.

Our booth was THE place to be on the show floor. Every day, the industry's top technologists and authors could be found in our booth—conducting interviews, being interviewed, or just hanging out and talking about the show.

Our booth stayed packed with industry movers and shakers, in spite of our location at the rear of the venue, where the booth numbers were out of order. It helped that we had Donald Trump's cutout standing near the aisle, giving passersby the twin thumbs up. Donald was an unofficial partner of ours; he had people wanting to pose with him, either shaking his hand, or, in Joe Fjelstad's case, attempting to strangle him. We had to keep an eye on Donald. Last year at APEX in San Diego, someone adopted our "World's Most Inter-

esting Man" cutout, and we didn't want Trump to wind up in the trunk of someone's rental car, out in the desert.

Before the show opened, our IT guys successfully conquered the challenges they faced to power the three flat-screen wall monitors that featured our articles, photos, and customers' logos in rotation. The monitors were visible from halfway across the venue, which served us well because our booth was in the back of the venue near the loading dock. Our customers got a kick out of seeing their logos pop up on the screens.

And like a good touring band, we handed out merchandise. Every interviewer and interviewee

received an I-Connect007 button, and we gave out 007 stickers, too. We almost ran out of "merch."

Some of you may not be aware of this, but we also had a crew in Shanghai providing Real Time video

2016

Interview

coverage of the CPCA which Show, was somehow scheduled the same week as IPC APEX EXPO. There are 52 weeks Connect to choose from. How on earth did those big industry shows end up in the same week? Our production crew worked overtime that week! It's hard to top the presence we have at a show.

On the conference side, the Design Forum was a big hit. Keynote speaker Dale Parker of Google X gave an awesome presentation that focused on Google's driverless cars and other just plain cool stuff. He stressed that Google X won't take on a project unless they believe that it can achieve a 10x increase in productivity, compared to most companies that are excited to see a 10% increase for any project. Parker, a former PCB designer at Shure, then called on the PCB design tool vendors to throw out all of their 1990s-era code and redesign their software from the ground up.

And as Parker pointed out, the EDA companies will eventually have to build artificial intelligence into their flows if they want to truly increase their tools' performance. Would you like to see AI in your favorite design tool? The tool vendors I spoke with were noncommittal when I asked if they'd be scrapping their existing code soon, or introducing AI. Some designers would say there's already too much AI built into their tools.

It was a busy but fun week. And to top it off, our own Patty Goldman, managing editor of The PCB Magazine, was inducted into the IPC Hall of Fame. Congratulations, Patty!

Next year, we're back to San Diego for IPC APEX EXPO. It's going to be hard to top this year's event, but it's hard to have a bad time in San Diego.

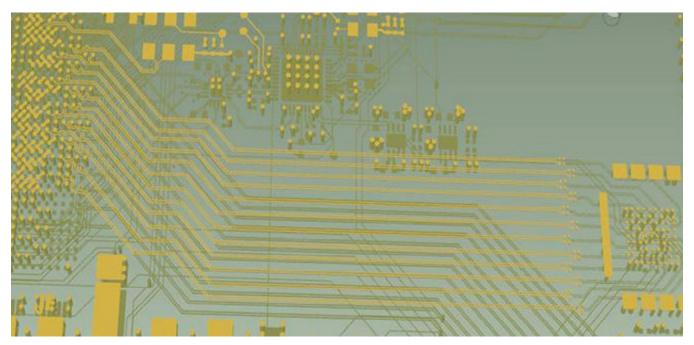

#### **Of Designers** and Engineers

When we survey our readers and ask them to name their biggest challenges, PCB designers sometimes name their design engineers as the main culprits. It happens often enough that it got us thinking. Why is there a split between some PCB designers and their design engineering coworkers? Some designers and EEs blame it on a simple

lack of communication. And more engineers are performing PCB design and layout now. Some designers see them as angling to take over their jobs.

So we asked some engineers and designers to discuss the reasons for the divide, and what can be done to address this problem. This month we have a variety of feature articles, including a cover story by design instructor Rick Hartley, a man who's been known to tell it like it is. We also have a feature by Analog Home's Steve Hageman, as well as interviews with lead designer Andy Critcher of Total Board Solutions and Randy Faucette, director of engineering at Better Boards Inc.

This was one of the most interesting topics we've had lately. Is there a schism between your company's designers and design engineers? Read on, and please let me know what you think! **PCBDESIGN**

Contribu

Andy Shaughnessy is managing editor of The PCB Design Magazine. He has been covering PCB design for 16 years. He can be reached by clicking here.

# **Working with Circuit Design Engineers**

#### by Rick Hartley

RHARTLEY ENTERPRISES

*The PCB Design Magazine* and PCBDesign007. com receive a lot of feedback from reader surveys. One frequent comment from both PC board designers and circuit engineers involves the frustration of working with each other. Also, a question often asked is, "Are EEs taking over PC board design?"

In 1965, with a two-year college degree, I began life in electronics as an R&D technician. Over a few years I became a circuit designer (EE). Several years later I took another fork in the road, moving into PC board design and layout, making the assumption that, "Being an EE, surely I would be a better board designer than most." Yeah, right!

I quickly learned that PC board design in the 1970s was less a matter of engineering and more a matter of art. Clearly there was science involved but that science was much more about mechanics and manufacturability of bare boards and assemblies than about electronics. People who understood the value of copper balance, pad-to-hole ratio, hole-to-board thickness ratio, how component placement impacted assembly and repair, knowledge of thermal transfer, etc. made better board designers than those with knowledge of only circuit theory. Those who had good analytical ability truly had the ultimate tool needed for board design. But knowledge of electronics, who cared? My education and background meant very little; I was learning everything from scratch.

Is this still true today? We will attempt to answer that question. Why did EE knowledge play such a small role back then? Circuits in those days, with the exception of the RF world, were so low in frequency that board traces had to be several yards long before they were a distributed length, capable of impacting performance. You could, by today's standards, make every mistake under the sun, even in very large boards, and there was a good likelihood the circuit would work anyway. This was not always true, but it

# STRVING FOR EXCELLENCE IN EVERYTHING WE SAY AND DO.

- Prototype to Production

- Time Critical Production

- Commitment to Customer Service

- Best Quality & Delivery Performance

- Fair and Competitive Pricing/Costs

- Rapid Response to Quote Requests

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

**Tour our Facilities**

View our Capabilities

The Absolute Best Value in High Technology Circuit Boards 847.891.5800 • www.eagle-elec.com

MANUFACTURERS OF QUALITY PRINTED CIRCUIT BOARDS

was true most of the time. My electronics background occasionally offered some advantage, but those occasions were rare.

#### **The Seeds of Friction**

From the 1950s to the late 1980s, our board design methods were severely bending the laws of physics, teetering on the edge of disaster! A lot of today's grey-haired designers cut their teeth on the layouts of that period and got used to working without input from engineers. Many of those PC board designers were converted technicians, mechanical designers, and artists who learned to read a schematic and mastered artwork taping. EEs would often give their thoughts on what should be done, but you could listen to them or ignore them and the circuit would likely function either way. This era created some tension between board designers and their EE counterparts, mostly because they completely ignored each other's ideas.

This era created some tension between board designers and their EE counterparts, mostly because they completely ignored each other's ideas.

In the early 1990s, industry as a whole started to see circuits that did not always function as intended or had EMI problems. By the late 1990s, this bad behavior had increased dramatically. It did not take long before we realized that poor board layout was the culprit. The layout practices we used for decades were no longer acceptable in many designs. We had gone from bending the laws of physics to violently breaking them. Why? ICs were getting much faster, due to output rise and fall time getting much shorter. Because of faster outputs, normal line lengths, regardless of clock frequency, were more likely to cause ringing, crosstalk, noise, increased EMI, etc.

During this period many of the PC board designers who possessed little knowledge of electronics grew to rely on circuit engineers to help guide component placement, since many EEs better understood which ICs and circuits were likely to cause problems. This, and the use of multilayer boards, reduced the problem for quite a few years, which gave the perception that "knowledge of circuit theory made a better board designer." Though things were better during this period, I was involved in many designs that failed EMI testing, even though the company circuit engineers and I reviewed and approved the layouts. Though circuit knowledge helped us, it was not enough to stop the problems. Clearly we were missing something important!

IC outputs today are so fast that the problem has become an epidemic. Almost all ICs in production have rise times and fall times well under 1.0 nanosecond, mostly in the range of 300–700 picoseconds. This reality makes any transmission line (trace and its return path) longer than 0.5" to 1.0" (13 to 25 mm) a potential problem. In short, everything is high-speed, capable of causing SI, noise or EMI problems. All this simply means that every PC board of today has to be laid out to satisfy the laws of physics.

What does this have to do with PC board designers and engineers working together? Both groups know there is a real possibility that each design could have problems caused by board layout. Many engineers believe their knowledge of circuit theory is the solution. Many board designers believe the information gained from IC app notes or eval circuits offer a solution. The fact that the two groups disagree says, "At least one party is wrong." My consulting experience has shown that, much of the time, both parties are wrong.

One assumption is often made by both groups: "XYZ layout practice has always worked, so it must be right!" Well, the layouts we did in the '70s and '80s worked but they were far from right. Many circuits work but fail EMI testing, or they work initially but stop working a few years later, after ICs with faster outputs are released. These issues and many others show that the layout did not properly satisfy the laws of physics in the first place. Never use past practice as proof that some method is correct!

#### It's Hard Out Here for an EE

There is one thing that frustrates many circuit engineers: They are usually held responsible for the entire success of a system. Even though they do not do the packaging design or the board layout, they are held liable when hardware-related problems occur that are caused by those design features. EMI is almost always the result of a physical entity causing resonance and radiation, yet circuit engineers are often not allowed to control these physical items. They want to put in their two cents' worth, and rightly so. Most board designers understand that, but they believe, "If you are going to put in your two cents, make sure you actually know what you are talking about." It is OK to be heard, but it's not OK to tell the board designer to do this or that when you really do not understand the problem. Far too many engineers do not understand the cause of the problems that designers see every day.

This goes for board designers as well. If you are going to push back at your engineer's suggested layout ideas, make sure to base your thinking in physics, not in some half-baked idea that came from an app note or a poorly designed evaluation board (this is fodder for another article).

It is very important to know, schematically, how a circuit will function, "what drives what," "what is dependent on what," and what timing issues are critical. These are things you should understand whether you are a circuit engineer or a board designer. Not having an EE degree does not relieve designers from the absolute need to understand basic circuit behavior. If you do not know, ask! However, knowledge of these things, alone, will not eliminate the risk of SI or EMI problems. There is much more to this issue.

So, what is the solution to good PC board design? One thing has held true over the decades: Understanding how to design to maximize manufacturability, testability, ease of repair, and good thermal transfer has not changed and probably never will. Board designers will always need to know about these issues. Of this, most designers and engineers agree. Is knowledge of electronic circuit theory necessary to lay out sensitive transmission lines and complex power delivery? No! Knowledge of circuit theory does not hurt your cause but, by itself, is not the solution.

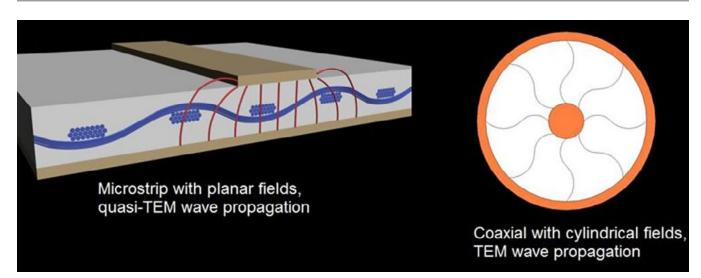

What you need to know is elemental electromagnetic field theory. The problem is not about voltage and current; it is about EM waves moving through transmission lines. Folks who understand this have their arms around the real problem.

What you need to know is elemental electromagnetic field theory. The problem is not about voltage and current; it is about EM waves moving through transmission lines.

Thanks to guidance from friends like Ralph Morrison and Dan Beeker, I have understood this for many years and now know the real solutions. Once this knowledge settled into my little brain, I suddenly realized exactly what causes problems in PC boards and what to do to avoid them. Everything became crystal clear! Where do you stand? Consider the following:

- Current in a transmission line forms in the copper, but the energy of the line is not in the copper.

- Energy in transmission lines moves through the plastic insulation of the board, the space between the copper features.

- Current formed in vias is all on the outside of the via barrel. No current flows on the inside of a via.

Those three simple statements tell us a lot about why problems occur in some boards and not in others. If any of those comments sound foreign to you, whether you are a circuit engineer or a board designer, you must read a good book about fields in PC boards, or run, don't walk, to the next PCB West Design Conference. This is not a sales pitch for PCB West, but it happens to be a great venue for such training. There are other excellent conferences, as well as books and other publications that can provide this information.

Are engineers taking over board design? Those able to stay awake when Maxwell's equations hit the blackboard, who were conscious when field theory was introduced, do have a leg up over folks who do not possess this knowledge. Many of the new board designers will likely come from the EE community, but it is certainly not necessary to be an EE, as long as you understand the real issues.

As mentioned, items associated with elemental field theory can be learned at conferences or from books. This and how it applies to PC board design is what you most need to know to be a great board designer, one who lays out 'noise free' circuits. Aside from field theory, as mentioned earlier, every good designer needs knowledge of manufacturability, testability, etc. So, you want to get along at work? Have the EE and PCB groups collectively learn how and where energy travels in PC boards (field theory). Using that knowledge, decide how the boards should be properly stacked, routed, etc., to take advantage of the natural condition of EM wave movement. Once you do this, designs will work and pass EMI testing and there will be no more tension between the EEs and board designers, at least not over board layout, and you can both stop designing from app notes, rules of thumb and voodoo techniques.

And remember: We're all in this together! **PCBDESIGN**

**Rick Hartley** is the founder and principal engineer of RHartley Enterprises, through which he teaches and consults to eliminate SI, noise and EMI issues in PC board design. Rick can be reached by <u>clicking here</u>.

### Hannover Messe: Industry 4.0 Has Become a Reality

"Integrated Industry - Discover Solutions" is the slogan of this year's Hannover Messe, which will open its doors on 25 April. Member companies and the VDMA can present a great number of solutions for the workings of the factories of the future and for making Industry

4.0 a reality in Hanover. "Industry 4.0 has become a reality with intelligent products, production lines and value chains," says VDMA Executive Director Thilo Brodtmann. New business models for digital and interconnected production are being developed across the board and will be put on display in Hanover. "Anything you see at the stands there can be profitably deployed in your business. Thanks to its specific and profound knowledge of production and customer needs, German mechanical engineering has the edge here," Brodtmann points out.

In numerous presentations, discussions and press conferences at this year's Hannover Messe, the VDMA will make it clear that mechanical engineering stands at the heart of the tremendous

changes that will shape commercial life in the years to come.

The modernisation of the economy is also being promoted forcefully in the partner country of this year's Hannover Messe, the USA, under the catchphrase "Internet of Things." "But we have nothing to fear from the Americans," stresses Brodtmann. "We are in a good position in this race, and at some point the approaches on both sides of the Atlantic will coalesce into one giant whole."

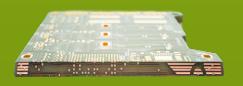

# Silicon Valley's LEADING Full Turnkey PCB Manufacturer

### FABRICATE & ASSEMBLE – ALL IN HOUSE

- Rigid PCBs 2-60 Layers

- Simple to Industry-leading Technology

- Quick Turn Prototypes and Production

- Proprietary Wrap Plating Process for Unsurpassed Reliability

### ASSEMBLY

- Latest FUJI Equipment

- 100% SPI Standard

- 100% AOI Standard

- 100% 2D/3D X-ray Standard

To Request a Quote through our website and enjoy NO tooling, programming, or stencil costs, <u>Click Here</u>!

$\mathbf{0}$

www.gorillacircuits.com

ISO 9001:2008 - MIL PRF 55110/31032 - ITAR

# The Roles of the Designer and the Design Engineer

#### by Andy Shaughnessy

Steve Hageman has been designing electronics since elementary school. An engineer by trade, he has decades of experience performing PCB design and layout. He spent years at HP, Agilent and Calex before hanging out a shingle for his engineering company, Analog Home. As someone who wears engineer and designer hats, Steve was a natural for this month's issue. I asked Steve to give us his opinion about the divide between some PCB designers and their engineers, and what can be done to solve this problem.

### **Andy Shaughnessy:** Steve, tell us a little bit about your company and how you operate.

**Steve Hageman:** I have experience working for companies of 50 people, to working for a company with 10,000 employees, to working as an individual contributor solving my specific customers' problems. As most engineers will agree, solving specific customers' problems is perhaps the most rewarding.

**Shaughnessy:** A recent survey of our PCB designer readers found that there's often friction between PCB designers and engineers. Some designers say their EEs are their biggest challenge. Why do you think there's such disconnect?

**Hageman:** I remember a quote by David Packard: "Follow the advice that Abraham Lincoln gave himself: 'If I don't like this man, I have to get to known him better.'" I have found that to be very true. Mr. Packard also knew that to get along with others you had to understand what they face as challenges. Taking the time to see the other person's point of view is very hard to day with the crush of schedules that we all have.

I think the biggest disconnect is the schedule compression that happens. We all know how this goes: The design takes longer than expected, so the PCB start date is pushed out, but the PCB delivery date is not changed, hence the poor guy that is last on the schedule has his schedule compressed beyond belief. By then, everything is rushed and things fall through the cracks. And what falls through the cracks typically is the EE design constraints.

# OrCAD Capture

105

108 109 17

1.6

1.4

23

21 20 19

#### Start Your Next Project The Right Way

Don't let budget concerns keep you from starting your next project with the most popular schematic capture tool on the planet. Get access to the fully scalable PCB design solution that can grow with your business.

The PCB folks are also pushed by manufacturing and these manufacturing rules are oftentimes only vaguely known by the EEs, hence they don't know what to allow for.

At very large companies there is a third entity pushing the PCB layout: the EMC/safety folks. Again, more constraints and rules that the EE may only vaguely know about. All of this comes together with schedule compression and causes the PCB folks to have to redo portions of the design to meet all the known and unknown design constraints.

Redoing work is never fun for anyone, especially when the time demands are so great. The only solution that I know of is to learn from the uncovered serious problems and with the team decide a path forward to try to prevent these from happening again in the future. And then try to stick to the plan.

### **Shaughnessy:** What do you think is the proper role for a PCB design engineer?

**Hageman:** The design needs to be sound and well specified, and a floorplan of the design needs to have been at least thought about that takes into account all the stakeholders' design constraints. Hopefully then the PCB design can be started. Checkpoints should be built into the system. While this seems to add extra time, I find that it really doesn't if it prevents rip-up and retry on the part of the PCB designer.

# **Shaughnessy:** What do you think is the proper role for a PCB designer?

**Hageman:** Putting on my PCB designer hat, I would need to make sure that what is given me is complete. The design has been reviewed, that is, the other stakeholders have had a chance to look at the floorplan and have had a chance to make inputs. Then the PCB design can start. I find that having many checkpoints along the way works best. But stuff will go wrong and we all need, as the beer commercials say, "to stay frosty."

**Shaughnessy:** Some PCB design tools are marketed directly to the design engineer, not the PCB designer. Do you think PCB designers are being squeezed out?

Steve Hageman

**Hageman:** I'm sure it happens both ways. In the larger companies I have worked where there are PCB layout groups or services, I have found that the PCB groups usually have the most say on tool sets. Basically everyone wants to use the tool that they know and can work with. This is only natural. Making sure that there is adequate training can help those on both sides that feel left out of the loop. Training today can be provided very cost-effectively by the tool set vendor or their FAEs.

#### **Shaughnessy:** With more and more engineers doing PCB design work (some PCB design and layout classes are 50% EEs), what do you think is the solution to this friction?

**Hageman:** I personally like doing my own PCBs; I always have, but some engineers really don't like doing this work. It's a point of personal preference. In small companies you might be forced to do your own designs and in a large company

# **TECHNOLOGY** FROM COAST TO COAST

# Metro Circuits Speedy Circuits

For over 40 years, we have been producing advanced solutions for our customers in many industries across the globe including Defense, Medical, RF/Microwave, Semiconductor and Down Hole Exploration, among others. How can we add value to your next project?

LEARN MORE CHECK OUT OUR CAPABILITIES  $\mathcal{P}$

**PJC** Technologies Inc.

Two Facilities. **One Integrated Solution.**

EAST COAST Metro Circuits 585.254.2980

WEST COAST Speedy Circuits 714.898.4901 you might be prevented from doing your own designs. Companies have broad expectations and rules also. This shouldn't be a point of friction; it should be mutual work toward getting the job done. In my experience this has only been a sore point when the PCB-specific folks felt like their jobs were going away. I don't think this will ever happen as I have found that only about 1/3 of EEs want to do their own layouts. We can and should help each other out in getting to that end goal: solving our customers' problems.

**Shaughnessy:** Is there anything else you'd like to add?

**Hageman:** My experience at Hewlett Packard was the best as far as teams go. There was no blame, if anyone stumbled and fell, the rest of the team would pick the guy up, dust him off and we would all get on with it. I try to remember and mimic this behavior as much as possible. I also find that keeping focused on who is paying the bills, namely our shared customers, helps in keeping the inter-team friction down. It doesn't always work, it isn't easy and it needs to be worked on continually.

#### **Shaughnessy:** Thanks for your time, Steve.

Hageman: Thank you, Andy. PCBDESIGN

### And the Survey Said: What are Your Pain Points?

As you all know, we survey our readers fairly often. We want to know what's going on with PCB designers and design engineers, especially the challenges and pain points that you all face.

After we sift through the percentages, we focus on your comments. The comments are a source of great information. They may be emotional, unscientific, and sometimes rambling comments, but it's accurate and from the heart.

I recently asked my readers to name the biggest challenges that they face every day. Here is a sample of the comments. Do these sound familiar to you?

- Lack of time (too tight production deadlines) and on time feedback from the clients (often resulting in massive amounts of extra work). Not getting timely feedback from initial testing. Our policy against slapping the snot out of idiots.

- Getting people to attend design reviews.

- Things like solder mask defined pads in some areas and copper defined in others, with PCB suppliers using global copper defined rules, lack of understanding of the soldering process in things like wave solder.

- Making symbols and cells for our CAD system.

- Meeting SI requirements for signal integrity. Placement of critical components within very tight areas and still meeting DFA requirements.

- Defining the stackup and impedance critical signals without a good tool. Getting a PCB description

direct out of the tool.

- Time to market! Engineers can get too involved in the little details, and fail to achieve time to market goals.

- Feature creep from the customer to the senior engineer and the designer.

- Electrical constraint requirements not described in schematic.

- Not enough man-power.

- Specifying alternative parts (second and third sources). Critical areas (noise, heat, vibration, etc.) indication. Lack of useful communication on what the designer and EE consider important to the design.

- Bean-counter management types who don't understand today's challenges.

- Manufacturability, testability, and reworkable design, as parts get smaller, with high-density pinouts.

- Keeping cost of fabrication reasonable using fine-pitch devices, i.e., avoiding blind and buried microvias for devices 0.5mm pitch or less.

- HDI technology with several via types. Definition of power/ground systems for better EMI. High-speed signals. Ceramic boards with thinner tracks. Embedded parts.

- Real estate, signal noise, and thermal electric offsets.

- More things to pay attention too. Power drop with in the PC board due to low voltages now. Thermal dissipation from small package with higher wattage use.

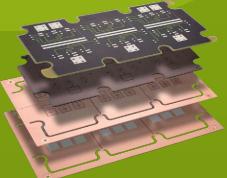

Flexible, reliable

Supply Chain Solutions

High quality copper

clad laminates ぐ

prepreg bonding materials

Ventec International Group is a world leader in the production of high quality and high performance copper clad laminates and prepregs, with full R&D and product development capabilities.

Our global distribution means we can readily supply our products to all markets in all geographic areas.

# Ventec – wherever technology takes you, we deliver

#### Ventec International Group

China: joan@ventec.com.cn Europe: contact@ventec-europe.com USA: ordersCA@ventec-usa.com

#### Follow @VentecLaminates

www.venteclaminates.com

# Designers and Design Engineers: Two Sides of the Same Coin

Andy Critcher, TBS

#### by Andy Shaughnessy

Andy and Sue Critcher have been the lead designers at Total Board Solutions Limited, an UK-based design bureau, since its founding in 1998. I asked Andy to share his opinion about the friction between some PCB designers and their engineers, and what can be done to improve communications between these groups.

# **Andy Shaughnessy:** Andy, tell us a little bit about your company and how you operate.

**Andy Critcher:** Total Board Solutions Limited (TBS) is a design services bureau based in the UK. We fit into our customer's design process, providing whatever is not a core competency. This means that for some customers we perform just the layout portion of their design while for others we enter the schematic, libraries, create the layout and even get the boards fabricated and assembled—no two customers are exactly the same. When working with startups we provide the link between the concept, or idea, and prod-

uct realization; providing knowledge of design process, fabricators capabilities and our experience when discussing the inevitable tradeoffs between the requirement and what is possible.

**Shaughnessy:** A recent survey of our PCB designer readers found that there's often friction between PCB designers and engineers. Some designers say, only half-jokingly, that their EEs are their biggest challenge. Why do you think there's such disconnect?

**Critcher:** Looking solely from the PCB side, I think that the disconnect mainly arises from the lack of understanding of what a PCB designer actually does, it is perceived as a simple task of dot joining and that anyone can do it. I know that this is a bit of a cliché but it does seem to hold true. As an example, in a number of the companies that I have worked with, PCB progress meetings are held and the PCB designer is never asked to attend; their input can be easily be determined by the engineering team/project manager.

# Managing a global PCB supply chain can seem like a puzzle.

# Let us be the solution.

With over 35 years of experience and key partnerships around the world, we have what it takes to make your next project on time, on budget and hassle-free.

LEARN MORE ABOUT THE NUJAY SOLUTION **O**

www.nujaytech.com

This perception is backed up by the lack of formal qualification for PCB designers—for my generation, we generally started off as mechanical draughtsman in the traditional drawing office and then moved to the PCB section.

This perception means that the status of the PCB designer is quite low, so when they advise the engineer that something is not possible this can be met with a certain amount of derision. The engineer possibly thinks that the PCB designer is just being obstructive, while conversely, the PCB designer thinks that the engineer is very dismissive of his knowledge, capabilities, opinion, etc.

The engineer possibly thinks that the PCB designer is just being obstructive, while conversely, the PCB designer thinks that the engineer is very dismissive of his knowledge, capabilities, opinion, etc.

Let's look at the issue from the engineer's perspective. By providing design consultancy, we are fortunate enough to be a lot more involved in the engineer's world, including some of the problems that they have to deal with as part of the overall product development. One engineer explained that the design part was relatively straightforward, but the need to meet cost, functionality, component sourcing, obsolescence, test plans, as well as reading through 150+ pages of documentation on a device's timing "makes life interesting." As PCB designers, we tend to have a lot of questions, especially about the newer technology, so we can bombard the engineer with a number of questions concerning unfamiliar topics expecting immediate answers, and normally at this point the pressure to get it finished is already building.

### **Shaughnessy:** What do you think is the proper role for a PCB design engineer?

**Critcher:** This is a difficult one to answer. There are so many aspects of the design engineer's role that are not obvious to the PCB designer, such as component selection, obsolescence management, test plans/specs, etc. I thought that I would answer this question in relation to their interaction with the PCB designer.

The definition of the circuit itself goes without saying; the engineer should also drive the PCB layout with the necessary constraints to ensure that the PCB will function to within spec. So, together with the circuit diagram the engineer should also indicate the following (this list is not exhaustive)

- a. Impedance requirements

- b. Trace length/matching requirements

- c. Current handling requirements

- d. Stackup requirements

- e. Placement constraints

- f. Connector locations

- g. Board outline (could be the mechanical engineer)

Depending upon the software and the individual company process, the engineer may be able to enter these constraints directly into the schematic capture tool.

### **Shaughnessy:** What do you think is the proper role for a PCB designer?

**Critcher:** The role of the PCB designer is to take the data from the engineer and create the layout, drawings, fabrication and assembly data while adhering to constraints and the relevant standards, including both company, IPC and any specific to the manufacture.

The PCB has many outside influences such as enclosure, thermal, EMC requirements that may not be under the remit of the engineer so they should also liaise with these people or teams.

Essentially the PCB designer takes all the design requirement inputs from the various sources and then has to find a solution that hits as many as the requirements as possible. At this

# VERIFY **OPTIMIZE** ANALYZE PREPARE PANELIZE COMMUNICATE DOCUMENT

# **Ensure PCB Manufacturing Success!**

**CAM350**°

Verify and Optimize PCB Designs for Successful Manufacturing.

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

@2016 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB design post processing needs.

#### Visit downstreamtech.com or call 800-535-3226

point the PCB designer essentially drives the physical design.

I think that to be effective in this role it helps to have a working knowledge of signal integrity, power integrity, and RF and analogue layout techniques. In my experience, I have found that in larger companies, there is a level of specialization for engineers; this tends not to be the case for PCB designers so they are "au fait" with multiple disciplines.

The PCB designer should also keep up with the latest technologies for components, board fab and assembly.

**Shaughnessy:** Some PCB design tools are marketed directly to the design engineer, not the PCB designer. Do you think PCB designers are being squeezed out?

**Critcher:** In general the answer is no; in my experience I find that this may be practical for smaller design teams or for less complex PCB layout, but when the design is either mixed-technology (RF, digital and analogue) or a complex layout with large component and net counts, a dedicated PCB designer is the most successful solution.

There are a number of reasons why I think this. Firstly, it is NOT that the engineer is not capable of performing the layout task, but more with regard to the pressures on design teams to deliver on time to meet the time-to-market requirements most design teams need to parallel as many tasks as possible, layout included.

Further to this, the schematic is generally a living document that evolves as the layout proceeds due to marketing requirements or simulation results, etc.—the engineer cannot perform two discrete tasks at the same time to maximize the time efficiency of the design team as a whole separating the two tasks makes sense.

On a practical side, the electronic engineering teams are generally split via the design disciplines already mentioned—RF, analogue and digital—would this mean that each engineer would take it in turns to layout their section?

The PCB tool set is a complicated environment; although the new breed of tools provide ways to support the entry of the complex data sets such as constraints, the complexity continues to increase ahead of the tools. Essentially the environments are not really for the casual user. The automation of the applications increases but the need to enter the constraint data and drive the tool successfully requires the user to use the toolset day-in and day-out to be efficient. In many instances the engineer could spend a few weeks to over a month away from the tools themselves as they test and commission the PCBs.

66 In many instances the engineer could spend a few weeks to over a month away from the tools themselves as they test and commission the PCBs.

Another area that the PCB designer has a certain amount of experience is in the actual fabrication and assembly process; this is generally accumulated over a number of years working with these disciplines. Pre-preg suitability etc., all goes into the pot.

The PCB designer spends a lot of time taking input from different engineers and this helps hone their skill set; taking input from multiple sources helps the designer solve future problems by being able to draw on the gathered experience from the different sources.

In the same way that many companies have a dedicated signal integrity team, the idea of a dedicated PCB makes sense for the same reason.

**Shaughnessy:** With more and more engineers doing PCB design work (half of the attendees at some PCB design and layout classes are electronics engineers), what do you think is the solution to this friction?

**Critcher:** I think that the solution to the friction is communication, integration and pa-

# PCB fabrication, assembly, and free award-winning CAD design software.

Leading the industry for over 40 years as the preferred *prototype and production PCB solutions provider* for design engineers.

#### WE ALSO OFFER:

- Best overall quality, value and competitive pricing

- Design for Manufacturability Tool: DFMplus

- Fully supported and free PCB123® design software

- Integrated assembly services

- FREE Ground Shipping

- PCBs as low as \$28 with ValueProto®

**100%** On-time Guarantee

QUOTE NOW 🔰

#### Questions? Comments? Suggestions?

We appreciate hearing from you! Contact us at: 1-800-228-8198 or via e-mail at support@sunstone.com

tience; situations like this cannot be fixed overnight.

Over the years I have noticed that when I work with companies who have a 'design team' comprising electronic engineers, PCB designers, mechanical engineers signal integrity engineers etc. who are tasked with a specific board or product design there is less friction.

I have seen most friction when the 'teams' are divided by function/discipline rather than by project teams. I also tend to see that the team is more effective when the aims/goals are shared; this especially works well where a concurrent design process is needed.

### **Shaughnessy:** Is there anything else you'd like to add?

**Critcher:** I think that the ability to perform the design of the PCB in parallel across the design team today is critical in many cases. If we have a single person performing each individual task in series this would not help reduce the design time.

#### Shaughnessy: Thanks for your time, Andy.

Critcher: Thank you. PCBDESIGN

#### University of Sussex Research Brings 'Smart Hands' Closer to Reality

Using your skin as a touchscreen has been brought a step closer after UK scientists successfully created tactile sensations on the palm using ultrasound sent through the hand.

reverse - the waves become more targeted as they travel through the hand, ending at a precise point on the palm.

It draws on a rapidly growing field of technology

The University of Sussex-led study - funded by the Nokia Research Centre and the European Research Council - is the first to find a way for users to feel what they are doing when interacting with displays projected on their hand.

This solves one of the biggest challenges for technology companies who see the human body, particularly the hand, as the ideal display extension for the next generation of smartwatches and other smart devices.

Current ideas rely on vibrations or pins, which both need contact with the palm to work, interrupting the display.

However, this new innovation, called Skin-Haptics, sends sensations to the palm from the other side of the hand, leaving the palm free to display the screen.

The device uses 'time-reversal' processing to send ultrasound waves through the hand. This technique is effectively like ripples in water but in called haptics, which is the science of applying touch sensation and control to interaction with computers and technology.

Professor Sriram Subramanian, who leads the research team at the University of Sussex, says that technologies will inevitably need to engage other senses, such as touch, as we enter what designers are calling an 'eye-free' age of technology.

"Wearables are already big business and will only get bigger. But as we wear technology more, it gets smaller and we look at it less, and therefore multisensory capabilities become much more important," he says.

"If you imagine you are on your bike and want to change the volume control on your smartwatch, the interaction space on the watch is very small. So companies are looking at how to extend this space to the hand of the user. What we offer people is the ability to feel their actions when they are interacting with the hand."

# ULTRA HIGH THERMAL PERFORMANCE

Introducing SH-260, a new Polyimide system with Tg > 250°C (TMA)

### SH-260 IS IDEAL FOR:

- Burn-in boards

- Down Hole

- Aircraft and Aerospace

- Ultra-high count layer boards

- Other PCB high temperature/ long-duration applications

CLICK HERE TO LEARN MORE

www.paramount-usa.com

#### FEATURE INTERVIEW

# The Partnership: Design Engineers and PCB Designers

#### by Andy Shaughnessy

Randy Faucette is founder, president and director of engineering at Better Boards Inc. in Cary, North Carolina. Founded in 2003, Better Boards provides electrical engineering, PCB design, signal and power integrity analysis, and a variety of other services. I asked Randy to talk about some of the occasional tension between PCB designers and design engineers, and what he thinks can be done to help open the lines of communication.

### **Andy Shaughnessy:** Randy, tell us a little bit about your company and how you operate.

**Randy Faucette:** Better Boards is a PCB design and engineering services company. We specialize in all aspects of PCB design, but also provide electrical and mechanical engineering, software/firmware development, prototype and small-volume production manufacturing, and many types of analysis including failure mode, root cause, thermal, crosstalk and power integrity. We use a breadth of design tools including Cadence Allegro, Altium, Mentor Expedition and PADS. Our customers range from large companies like Lenovo and Cree to small entrepreneurs. We perform finite services our customers define to full development of products from concept to production. We cover many industries, such as medical, commercial, consumer, telco, and space/military.

**Shaughnessy:** A recent survey of our PCB designer readers found that there's often friction between PCB designers and engineers. Some designers say, only half-jokingly, that their EEs are their biggest challenge. Why do you think there's such disconnect at some companies?

**Faucette:** We have not found that to be true here at Better Boards. We approach PCB design from an engineering standpoint. The PCB designer should not just be a tools jockey hoping that engineering will tell them where to put parts and how to hook them up. The PCB designer should understand how the circuits flow, understand the different types of interfaces and how those need to be treated on the board, and un-

# Engineering And Providing Balanced Interconnect Solutions

Miraco, Inc. • Manchester, NH • miracoinc.com • 603-665-9449 ...connecting technology

**Randy Faucette**

derstand the manufacturing aspects as well (including test). The only challenge we experience with engineering honestly is playing the role of middleman between engineering and manufacturing. Engineering may want parts located too close to another component or too close to a through-hole pin, not allowing a proper wave soldering operation to be performed. Those drive costs and can affect reliability. If the layout designer is effective, engineering is happy and manufacturing is also happy. That makes the boss happy!

# **Shaughnessy:** What do you think is the proper role for a PCB design engineer?

**Faucette:** Outside of creating a correct schematic, the PCB design engineer needs to effectively communicate ALL of the requirements of the board and then review the board once designed to ensure all the requirements have been achieved. Some examples of requirements

would be interface impedances, timing rules, and power requirements. It's also important to identify high-speed nets, clock lines, sensitive nets/circuits, high-current buses, thermally hot nodes, high switching loops. The stackup is critical in most designs today and this must be considered early. One thing that should be communicated early on is the environment of the product and the expected reliability. The temperature and humidity can drive what component packages to use (or more importantly what not to use). The reliability can drive board technology and spacings. The best way to communicate all the rules is in a PCB requirements document. This is the scope of the layout. If it's in the document, it's important. It also removes the flurry of comments, instructions, and "Oh, BTWs" that tend to arrive in various emails and in cubicle conversations. It's a captive, living document to keep everyone straight. It's also it a perfect checklist at review time.

# **Shaughnessy:** What do you think is the proper role for a PCB designer?

**Faucette:** The PCB designer's role is to take the requirements (hopefully as spelled out in the requirements document) and create a layout that performs as needed electrically, but that can also be manufactured with high yield, and that will be reliable. The PCB designer should pull in all the mechanical requirements (outline, mounting holes, critical component locations, keepouts and other restrictions) and ensure form and fit are correct. The PCB designer should also ask all the questions to spark conversations so that all requirements can be discussed and documented early. At final review is not the time to find out that an ICT fixture is needed.

# **Shaughnessy:** Can you give us an example of how your designers and engineers function together?

**Faucette:** Early collaboration is key. Hopefully, every design provides the opportunity to learn and that knowledge can be implemented going forward. Learning never stops. As we grow in our careers, we become more and more effective and efficient in our roles. The result should

# Switch contact lubricants for superior performance

Our advanced contact lubricants provide increased reliability, enhanced electrical performance and extend the lifetime of switches, connectors and other current carrying metal interfaces by more than 300%.

Our development of domestic and industrial applications for the automotive, military and aerospace industries has led to range of contact lubricants with exacting standards and superior performance.

With a heritage that includes the invention of contact lubricants, we have spent over 70 years establishing an unsurpassed reputation for the manufacture and supply of innovative, industry leading specialist lubricants.

Isn't it time you discovered how Electrolube can serve you?

#### Tel: 888-501-9203 www.electrolube.com

Electronic & General Purpose Cleaning

Encapsulation Resins

**ELECTROLUBE**

THE SOLUTIONS PEOPLE

Maintenance & Service Aids

Scan the code to discover our full spectrum of superior Contact Lubricants and electro-chemical solutions.

be better performing hardware that's simple to build and that will last and be reliable.

**Shaughnessy:** Some PCB design tools are marketed directly to the design engineer, not the PCB designer. And more engineers are doing PCB design work—half of the attendees in some PCB design and layout classes are electronics engineers now. Do you think PCB designers are being squeezed out?

*Faucette*: If the PCB designers are being squeezed out, it's either because they are not doing their job or they are not being supported by management. If the engineer needs to explain how the flyback power supply should be placed and routed each time, then perhaps the engineer should just perform the work (if it takes an hour to sit with the designer to layout a power supply or it can take them an hour to just do it themselves, why spend two manhours when one will do?). However, the designer should not be squeezed out. The demand of the board performance is growing and that requires a different set of knowledge. The board need to run faster signals, carry higher currents due to lower voltages, and dissipate more heat due to smaller packages. We don't think it's realistic for engineering to keep up with that and take over the role of layout. The reality is that experience is key here. There are no classes in college that teach proper layout or electronics packaging. You may do a couple of layouts for a class project, but you can't replace 20 years of gained knowledge from having layouts be your primary function. Having said that, PCB designers need to stay up with the latest technologies, materials, manufacturing processes, IPC specifications, and component package trends.

#### **Shaughnessy:** A few designers who work great with their EEs say it all comes down to an unspoken agreement, an understanding of who does what. Is it really that simple?

**Faucette:** If they are both seasoned in their roles, then yes. The engineer does their job and delivers a good handoff to the designer and the designer carries it across the finish line. There is no way an engineer can layout a couple of boards a year and be a good layout person. Good layouts don't happen by accident. Sorry, tool companies.

# **Shaughnessy:** Is there anything else you'd like to add?

*Faucette:* Continuous education is critical. This is why Better Boards has gotten very involved in the local chapter of the IPC Designers Council and has been instrumental in the existence of PCB Carolina held in Raleigh each fall.

#### Shaughnessy: Thanks for your time, Randy.

Faucette: Thank you, Andy. PCBDESIGN

#### LOPEC 2016-Printed Electronics: A Key Technology of the Future

From April 5-7, 2016, LOPEC displayed pioneering and innovative products from the field of printed electronics in Munich, Germany. A total of 148 companies made their way from 18 countries to exhibit at the International Exhi-

bition and Conference for the Printed Electronics Industry. For the first time, Indian, Spanish, and South Korean companies were among the exhibitors. More than 2,000 visitors from over 40 countries attended LOPEC 2016. The key industry markets were also reflected in the most strongly repre-

sented nations in terms of visitors, which, besides Germany, were the UK, the USA and Japan.

# **RF/MICROWAVE CIRCUITS? AMERICAN STANDARD CIRCUITS MAKES IT EASY!**

Our experts are just one of the ways ASC makes buying PCBs easy. Your expert for RF/Microwave PCBs is John Bushie.

Have a question about designing your RF PCB? Click HERE to ask John now!

Digital RF/Microwave Flex/Rigid-Flex Metal Clad

**American Standard Circuits** Creative Innovations In Flex, Digital & Microwave Circuits

www.asc-i.com

#### DuPont, Taconic and PFC Team-Up for High-Speed Fle

At DesignCon, I sat down with three flex circuit specialists: Glenn Oliver of DuPont, Tom McCarthy of Taconic, and Steve Kelly of PFC Flexible Circuits. Our discussion covered a lot of territory, most notably the findings they described in the paper they were about to present later that day at DesignCon, and more.

#### Rex Rozario: The PCB Industry's True Renaissance Man

In this exclusive multi-part interview that was conducted recently, I-Connect007's Barry Matties will introduce you to all of the people that Rex Rozario is, and where he, his team, and Graphic PLC are headed to next.

#### <u>Happy's Essential Skills:</u> <u>Problem Solving</u>

Related to TQC and a very important role of an engineer is solving problems. Using a problemsolving methodology is a job that all engineers will use sooner or later, but if you are in product or process engineering in manufacturing, it will be sooner! This was the situation that introduced me to printed circuit manufacturing.

#### Happy's Essential Skills: Design of Experiments

Design of experiments (DOE) is one of the most powerful and influential engineering tools for product yield improvements, new products or processes development, or for problem solving. As mentioned in my last column, process problems led me to a career in printed circuits, and quickly solving those problems led me to a bonus stock award and a great life.

#### Manufacturing Institutes can Boost the Nation

In his most recent State of the Union address, President Obama highlighted a remarkable trend of recent years: the turnaround in many corners of America's manufacturing sector. Nearly 900,000 new jobs have been created by U.S. manufacturers in the last six years.

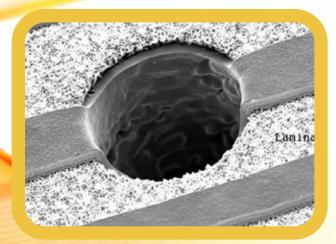

#### **Copper Via-Fill Technology in Development**

The use of via-in-pad technology is increasing rapidly in today's PCB designs. The need for miniaturization, combined with the rapidly decreasing pitch of component footprints, drives printed circuit board designers here. Via-in-pad requires the vias to be filled, planarized and then over-plated with copper.

# The Quiet Mainstreaming of HDI Manufacturing

Advances in technology continue to push the envelope of what's possible. And nowhere has the impact of those advances been felt more profoundly than in the evolution of the current class of mobile devices. Although design engineers have driven this evolution, the push to meet the associated manufacturing challenges has been responsible for a revolution in PCB manufacturing.

#### Weiner's World

Gene Weiner discusses PhiChem's upcoming open house event at its global HQ and R&D center in Shanghai during SEMICON China 2016, CPCA 2016 and productronica China 2016. He also focuses on the IPC Ambassador Council's plans to produce an executive forum in conjunction with IPC APEX EXPO 2017, IPC's association with Next-Flex, and much more.

#### The Sum of All Parts: The Cost of Quality

Throughout the decades, irrespective of industry or sector, markets have thrived on competition. They have, however, also relied upon some semblance of unity within their respective competitors. Industries rely upon their individual member companies' ability to work together for the greater good.

#### Rex Rozario, Part 4: A 10,000-ft. view of his Business Ventures, the Industry, and Life

In our final installment, Rex describes the common thread woven through all of his successful business ventures and varied interests: confidence and the fortitude to follow his dreams until they are realized. Rex also takes a look back at the evolution of the global PCB industry, and explains his approach to profitability, which includes building (and rewarding) a successful team.

SPONSORED BY:

ConnectO

GOOD FOR THE INDU

LAS VEGAS, NEVADA - MARCH 15 - 17, 2016

WWW.REALTIMEWITH.COM

# DDR3/4 Fly-by vs. T-topology Routing

#### by Barry Olney

IN-CIRCUIT DESIGN PTY LTD AUSTRALIA

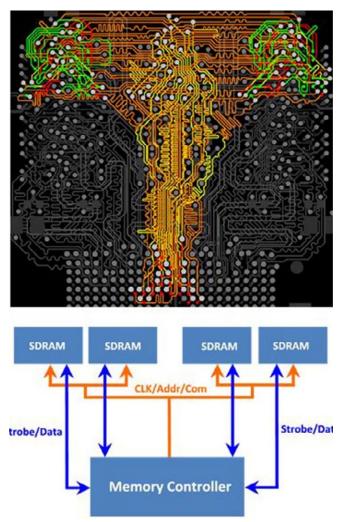

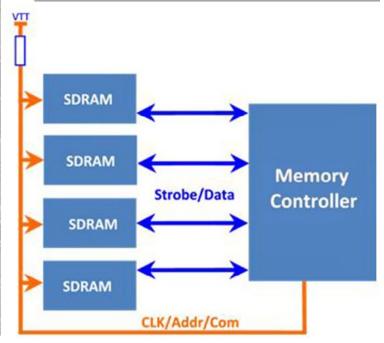

JEDEC introduced fly-by topology in the DDR3 specification for the differential clock, address, command and control signals. The advantage of fly-by topology is that it supports higher-frequency operation, reduces the quantity and length of stubs and consequently improves signal integrity and timing on heavily loaded signals. Fly-by topology also reduces simultaneous switching noise (SSN) by deliberately causing flight-time skew, between the address group and the point-to-point topology signals,

Figure 1: Double T-topology for clock/address/ command/control routing.

of the data groups. To account for this skew, the DDR3/4 controller supports write leveling. The controller must add the write leveling delays to each byte lane to maintain the strobe to clock requirement at the SDRAMs.

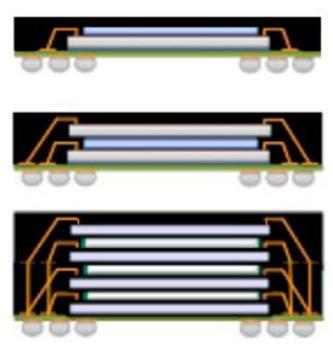

T-topology can be challenging to route, particularly double T-topology with four back-toback SDRAMs as in Figure 1, but it can be advantageous when using multi-die packages. The fly-by topology used in Figure 3 is much easier to route but does not work well with high-capacitance loads, such as LPDDR3 DDP (double die package) and QDP (quad die package) devices. IC fabricators basically arrange dies in parallel (as in Figure 2) to increase package density which can also increase input capacitance by up to four times. Excessive ring-back is often present in the first few nodes of the daisy chain.

This is the reason why the T-topology was developed. However, if you are supporting only SDP (single die package) devices, then the fly-by

Figure 2: SDP and multi-die DDP and QDP memory devices.

Intercept's complete design flow gives you the power to keep moving, full speed ahead. Use Mozaix for flexible schematic capture and Pantheon f or a dvanced, i ntuitive PCB/Hybrid/RF design to move quickly and seamlessly from concept to manufacturing. Our 30+ import transla tors make it easier than ever to switch tools. Let Pantheon and Moz aix drive your next innovation.

PANTHEON ADVANCED PCB, HYBRID, RF LAYOUT MOZAIX NEXT GENERATION SCHEMATIC CAPTURE REUSE BLOCK TECHNOLOGY MULTI-BOARD & PANEL ARRAYS LAYOUT-DRIVEN DESIGN & PROTOTYPING SIMULATION & ANALYSIS INTERFACES DESIGN AUTOMATION DFM & ARTWORK VERIFICATION HIGH SPEED DESIGN ARTWORK PANELIZATION AUTOMATIC DRAWING CREATION 30+ TRANSLATORS

www.intercept.com

30+ Years of EDA Software Solutions

is the most straightforward approach. It doesn't matter which topology you use, though—both fly-by and double T-topologies should work fine. If you are using a DDP device, then double-T topology works better than fly-by in terms of delivering a better system margin.

During a write cycle, using the fly-by topology, data strobe groups are launched at separate intervals to coincide with the clock arriving at memory components on the SODIMM or PCB, and must meet the timing parameter between the memory clock and DQS defined as tDQSS of  $\pm$  0.25 tCK. The PCB design process can be simplified using the leveling feature of the DDR3/4. The fly-by, daisy chain topology increases the complexity of the controller design to achieve leveling but fortunately, greatly improves performance and eases board layout for DDR3/4 designs.

It is not that you have to use fly-by write leveling, because it is a feature of DDR3 and DDR4, but rather that you have to use write leveling in order to allow fly-by routing. There is also no reason not to use the write leveling training for a T-topology in order to optimize the write strobe to clock timing. With this you can adjust slight differences in CA timings and avoid hard coding the skews that you normally have to manually take care of on the strobe to clock delay.

Fly-by topology is similar to daisy chain or multi-drop topology, but has very short stubs, to each memory device in the chain, to reduce the reflections. The double T-topology was used for DDR2 and had a downside in that the impedance discontinuities, due to branching along the traces, caused obvious margin losses. T-topology also tends to have overshoots, while the levels for fly-by are terminated and therefore do not reach the full swing voltage rails. Also, the length of the stubs has an effect on the maximum bandwidth of the transmission line. If you are employing high-frequency DDR4, then the bandwidth of the channel needs to be

as high as possible. With conventional T-topology, the trace stub is lengthened with an increase in the number of memory device loads. In some cases, there can be as many as eight memory devices connected to the processor. The resonant frequency or bandwidth is inversely proportional to the stub length.

$$fo = \frac{c}{4 x \text{ (stub length) } x \sqrt{Er}}$$

where fo is the resonant frequency, c is the speed of light and Er is the dielectric constant

The clock traces should be routed to a longer delay than the strobe traces per byte lane. This is necessary because:

1. The write leveling is capable of adjusting the clock to write data strobe alignment over a wide range, assuming the clock trace has a longer delay than the strobe traces.

2. The read leveling is capable of adjusting the read data eye to read the data strobe over a wide range. The adjustment is per byte, so board skew between the data and data mask signals should be minimized. 3. There is no automatic training for aligning command/address signals to the clock, but a fixed offset is programmable, in the processor, and can be used if necessary. Skew between the clock and address/control signals should be minimized.

Designing a memory interface is all about timing closure. Each signal's timing needs to be compared to the related clock or strobe signal in such a way that the data can be captured on both the rising and falling edge of the strobe—hence the term double data rate (DDR). The increase of data rates, to 4266MT/s for DDR4, has made the timing margin associated with each rising and falling edge much tighter. Even though a direct successor is not currently planned, sources speculate that the 5<sup>th</sup> generation DDR5 will use a serial interface to eliminate the issues associated with parallel busses. Serial busses are easier to scale up and have fewer connections, making PCB design less demanding.

It seems that every datasheet or reference standard you read on DDR design quotes different allowances for the timing budget. At a basic level, the differential clock is the reference signal for the address/control and command

| Parameter                                  | Setup (ps) | Hold (ps) |

|--------------------------------------------|------------|-----------|

| Open window from simulations               | 456        | 631       |

| SDRAM setup and hold times from datasheets | 25         | 100       |

| Slew rate derating if >1V/ns               | 2.3        | 2.8       |

| Timing offset with respect to Vref CA      | 13         | 11        |

| SDRAM derating                             | 88         | 50        |

| Crosstalk                                  | 47         | 42        |

| Controller error - skew                    | 200        | 200       |

| Clock error - jitter                       | 30         | 30        |

| PCB routing tolerance                      | 10         | 10        |

| Margin                                     | 41         | 185       |

Table 1: Example of the overall DDR3-1066 timing budget allowances and resulting margin.

|       | Planer p             |      |              |               |                                        |          |                       |            |                     |                |               |                        |             |             |

|-------|----------------------|------|--------------|---------------|----------------------------------------|----------|-----------------------|------------|---------------------|----------------|---------------|------------------------|-------------|-------------|

| Layer | 4 Layer              | 61.0 | er SLayer 10 | Layer 12      | Layer 14 Layer 16 Layer 18 Layer 10L N |          | 5                     |            |                     |                |               |                        |             | _           |

| UNITS | : mil                |      |              |               | 3/7/20                                 |          |                       |            |                     |                | Total Board   | Thickness: 6           | 5.32 mil    |             |

|       |                      |      | 2000         |               | Differential Pairs > 50/100            |          |                       |            |                     |                |               |                        |             |             |

| No.   | Via Spa<br>Hole Diar |      | Description  | Layer<br>Name | Material Type                          | Constant | 12 Signal R           | ght Time   |                     |                |               |                        |             | (B)         |

|       |                      |      | Soldermask   |               | Liquid Photoimageable                  | 4.0      | Signal                | Layer      | Laver               | Layer          | Trace Length  | Trace                  | Trace       | Flight Time |

| 1     | 8 4                  | 8    | Signal       | Top L_        | Conductive                             |          | Layer                 | Inductance | Capacitance         | Propagation    | (inches)      | Inductance             | Capacitance | (ps)        |

|       |                      |      | Prepreg      |               | N4000-13, 106; Rc=75% (2.5GHz)         | 3,19     | Number                | (nHim)     | (pFim)              | Velocity (m/s) |               | (nH)                   | (pF)        |             |

| 2     |                      |      | Plane        | GND           | Conductive                             |          | 1                     | 221        | 132                 | 1.85e+8        | 2.3000        | 12.91                  | 7.71        | 315.78      |

|       |                      | 11   | Core         |               | N4000-13 ; 106 ; Rc=68.3% (2.5GHz)     | 3.3      | 3                     | 265        | 160                 | 1.63e+8        | 2,3000        | 15.48                  | 9.35        | 358.40      |

| 3     |                      | 1.1  | Signal       | MidLa_        | Conductive                             |          | 4                     | 260        | 172                 | 1.58e+8        | 2.3000        | 15.19                  | 10.05       | 369.75      |

|       |                      |      | Prepreg      |               | N4203-13EP: 2016: Rc=54% (2.50Hz)      | 3.60     | 7                     | 260        | 172                 | 1.58e+8        | 2 3000        | 15.19                  | 10.05       | 369.75      |

| 4     |                      |      | Signal       | MidLa_        | Conductive                             |          | 8                     | 265        | 160                 | 1.63e+8        | 2 3000        | 15.48                  | 9.35        | 358.40      |

|       |                      |      | Core         |               | N4000-13 : 1080/106 : Ro+56.9% (2      | 3.6      | 10                    | 221        | 132                 | 1.85e+8        | 2.3000        | 12.91                  | 7.71        | 315.78      |

| 5     |                      |      | Plane        | PWR_          | Conductive                             |          |                       |            |                     | Total          | 13.8000       | \$7.16                 | 54.22       | 2087.86     |

|       |                      |      | Prepreg      |               | N4000-13; 7628; Rc=44% (2.5GHz)        | 3.84     |                       | 17X P      | lelative Signal Pro | onation        |               |                        |             | 2 22        |

|       |                      |      | Prepreg      |               | N4000-13; 7628; Rc=44% (2.5GHz)        | 3.84     |                       |            | State State State   | NCMON!         |               |                        |             |             |

|       |                      |      | Prepreg      |               | N4000-13; 7628; Rc=44% (2.5GHz)        | 3.84     |                       |            | - Internet          |                |               |                        |             |             |

|       |                      |      | Prepreg      |               | N4000-13: 7628: Rc=44% (2.50Hz)        | 3.84     |                       |            |                     |                |               |                        |             |             |

| 6     |                      |      | Plane        | PWR_          | Conductive                             |          |                       |            | 17                  |                |               |                        |             |             |

|       |                      |      | Core         |               | N4000-13 ; 1080/106 ; Ro+56.9% (1_     | 3.6      | Enter ea<br>time. Via |            | 3-                  |                |               |                        |             |             |

| 7     |                      |      | Signal       | MidLa.        | Conductive                             |          |                       |            | 8                   |                |               |                        |             |             |

|       |                      |      | Prepreg      |               | N4203-13EP: 2016; Rc=54% (2.5GHz)      | 3.60     |                       |            | 3 4-                |                |               |                        |             |             |

| 8     |                      |      | Signal       | MidLa_        | Conductive                             |          |                       | 0.71       | 4 7                 |                |               |                        |             |             |