an IConnect007 publication

The State of the Electronic Design Automation Nation p.10

The Case for Artificial Intelligence in EDA Tools p.24

Much More!

# **EDA Tools: Automation or Control?**

# **PCB BUYERS**compare nearly 1900 manufacturers now at The PCB List.

**Quick Search**

Advanced Search

The best way to find a PCB fabricator, anywhere.

### www.thepcblist.com

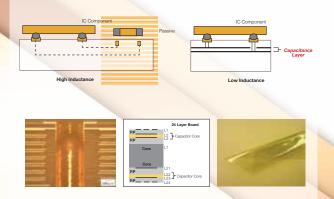

# **BOARD LEVEL** SIMULATION SPECIALISTS

ICD Stackup Planner - offers engineers/PCB designers unprecedented simulation speed, ease of use and accuracy at an affordable price

- 2D (BEM) field solver precision

- Characteristic impedance, edge-coupled & broadside-coupled differential impedance

- Unique field solver computation of multiple differential technologies per stackup

- Heads-up impedance plots of signal and dielectric layers

- User defined dielectric materials library over 28,000 materials up to 100GHz

ICD PDN Planner - analyze multiple power supplies to maintain low impedance over entire frequency range dramatically improving product performance

- Fast AC impedance analysis with plane resonance

- Definition of plane size/shape, dielectric constant & plane separation for each on-board power supply

- Extraction of plane data from the integrated Stackup Planner

- Definition of voltage regulator, bypass/decoupling capacitors, mounting loop inductance

- PDN EMI Plot with EMC Limits. Frequency range up to 100GHz

- Extensive Capacitor Library over 5,650 capacitors derived from SPICE models

## LEARN MORE

### www.icd.com.au

### May 2016

# **CESION** Feature Content

## EDA Tools: Automation or Control?

PCB designers get downright exorcised about their EDA tools. One point of contention has to do with automation itself: How much is too much? Some designers prefer manual control-not just for routing, but for much of the layout. Others want as much automation and horsepower as they can get. This month, our feature story by Intercept Technology's Abby Monaco highlights the challenges EDA software companies face trying to give designers the power, and control, that they need. UTC's Stephen V. Chavez explains why he prefers a mix of control and automation, and why mastery of each EDA tool is critical. Guest Editor Kelly Dack discusses why he prefers manual control for autorouting and more. And Barry Olney explains why artificial intelligence should be built into EDA tools from scratch, citing some of the repetitive tasks that could be addressed easily with AI.

- **10** The State of the Electronic Design Automation Nation by Abby Monaco

- 24 The Case for Artificial Intelligence in EDA Tools by Barry Olney

- 28 Design Automation Tools, Today and in the Future Interview with Kelly Dack

- 34 EDA Tools: Automation vs. Control Interview with Stephen Chavez

# **185HR** High-Tg, Low-CTE Materials with High Thermal Reliability

### **FEATURES**

- High Thermal Performance

- ▶ Tg: 180°C (DSC) (Base Laminate)

- ▶ Tď: 340°C (TGA @ 5% wt loss)

- Low CTE for reliability

- T260: 60 minutes

- T288: >15 minutes

- · Lead-free Compatible and RoHS Compliant

- UV Blocking and AOI Fluorescence

- High throughput and accuracy during PCB fabrication and assembly

- Superior Processing

Closest to conventional FR-4 processing

- Industry Approvals

- IPC-4101D-WAM1 /98 /99/ 101 /126

- UL File Number E41625

- Qualified to UL's MCIL Program

### **KEY APPLICATIONS**

- Heavy copper, 6 & 12 oz automotive applications

- Military

- Medical

- Industrial

- · Core Material Standard Availability

- Thickness: 0.002" (0.05 mm) to 0.060"/0.062" (1.5 mm)

- Àvailable in full size sheet or panel form

- Prepreg Standard Availability

- Roll or panel form

- Tooling of prepreg panels available

- · Copper Foil Type Availability

- Standard HTE Grade 3

- RTF (Reverse Treat Foil)

- Copper Weights

- ½, 1 and 2 oz (18, 35 and 70 μm) available

- Heavier copper available upon request

- Thinner copper foil available upon request

### · Glass Fabric Availability

- Standard E-glass

- Square weave glass fabric available

### **ORDERING INFORMATION:**

Contact your local sales representative or visit www.isola-group.com for further information.

Isola Group 3100 West Ray Road Suite 301 Chandler, AZ 85226 Phone: 480-893-6527 info@isola-group.com

Isola Asia Pacific (Hong Kong) Ltd.Isola GmbHUnit 3512 - 3522, 35/FIsola StrassNo. 1 Hung To Road, Kwun Tong,<br/>Kowloon, Hong KongD-52348 Dür<br/>Phone: 49-2Phone: 852-2418-1318info-dur@isinfo.hkg@isola-group.comIsola Strass

Isola GmbH Isola Strasse 2 D-52348 Düren, Germany Phone: 49-2421-8080 info-dur@isola-group.com

#

May 2016

Vol. 5, No. 5

thepcbdesignmagazine.com

### SHORTS

45 Small and Powerful: Pushing the Boundaries of Nano-Magnets

- 58 Spin Lifetime Anisotropy of Graphene

- 64 Five-fingered Robot Hand Learns to Get a Grip on Its Own

# **More Content**

### ARTICLES

- 52 Downstream: What a Long EDA Trip it's Been Interview with Joe Clark

- 60 Romanian Electronics Industry Celebrates 25th Anniversary of TIE by Joe Fjelstad

- 66 The Gerber Guide, Chapters 11 & 12 by Karel Tavernier

### COLUMNS

8

- The Designer Roundtable Roundup by Andy Shaughnessy

- **42** The Basics of Hybrid Design, Part 3 by Tim Haag

- 46 **Coatings: Five Essentials for Designers** by Phil Kinner

### HIGHLIGHTS

- 40 PCB007

- 50 MilAero007

70 Top Ten PCBDesign007

### DEPARTMENTS

- 72 Events Calendar

- 73 Advertisers Index & Masthead

# PCB Fab & Assembly Services from China's Experienced Manufacture

### More professional | More reliable | Quick turnaround | Less cost

## **New Customer Offer** Claim Now» Save **15%**, up to \$200 OFF Use Code: **PCBDE007**

### Our advantages -

- ☑ Fully ISO9001:2008, UL and RoHS certified

- ☑ Pro-PCB fabrication up to 32 layers

- Prototype to production

- Min. tracing/spacing to 3mil/3mil

- ☑ Min. microvias to 0.1mm

- Special PCBs-Aluminum, Flex & Rogers PCBs, etc.

- Small Qty full turnkey PCB assembly

www.pcbcart.com

sales@pcbcart.com

+86-571-87013819

# The Designer Roundtable Roundup

### by Andy Shaughnessy

I-CONNECT007

Every year, I attend SMTA Atlanta, just across town. You have to love a local trade show! No airlines, no jet lag, and no hotels. It's a small show; it would fit in a school gymnasium.

Regional tabletop shows like this may be the next big thing. Fees for exhibiting are so low that it's hard to justify not exhibiting. Some companies had their local reps manning the booths, but I talked to exhibitors who flew in from all over the East Coast, including one technologist from Canada. If you can tie in a few customer visits, the trip can pay for itself.

But for me, the highpoint of SMTA Atlanta is the Designers Roundtable. This informal gath-

ering usually draws about a dozen PCB designers, some of them ex-Scientific Atlanta veterans. It's moderated by UPMG's Pete Waddell, and we bounce questions off the designers for an hour or so. It's very informal, and it draws many of the PCB designers in metro Atlanta.

This year the roundtable had 15 attendees, up from 12 last year. Two of the new attendees were under 35, which surprised all of us. They design medical boards, which isn't such a surprise; that's one segment that keeps on growing. Most of the designers attending work for Cisco, Siemens, Sienna, NCR, and a few other smaller firms.

A few takeways: None of these designers thought much of solder mask-defined pads, because they create more problems than they solve.

• They don't trust CAD vendors' libraries, and there's not much love for OEMs' libraries either. One designer said he spends hours reinventing the wheel designing footprints he's used before.

• They didn't see much hope for the new "pay per use" license being floated by companies like ANSYS. One designer said that soon they'd all be back renting mainframe time like it was 1987 all over again.

• As always, most designers at the roundtable have a love/hate relationship with their EDA tools. One Cadence user said he really loves his tool's horsepower, but he's glad Dal Tools makes Cadence tools work better.

• None of these attending designers, or even their companies, use signal integrity or EMC simulation. One designer said, "All of the simulation in the chip is already done."

• Most of these designers don't like updating their EDA tools because each new rev of the tool contains even more errors than the previous rev.

I told the crowd about Dale Parker's keynote at the IPC APEX EXPO Design Forum. I asked what they thought about Dale's assertion that the 1990s-era code for most EDA tools should be rewritten from scratch, with native artificial intelligence built in. Most of them thought AI had no place in EDA tools. One designer said, "But we're the artificial intelligence!"

I was glad to see more designers attending the roundtable this year, and even happier to see some designers without a drop of grey hair. We're seeing more and more "youngsters" all the time. Is this industry finally turning hip and cool?

#### **Control vs. Automation**

This month, we take on a subject that's come up in various surveys we've conducted over the past year: How much automation is too much in your design tool? How much manual control should a designer have? Some of you appar-

ently turn everything off, and wish you could go back to hand-taping, while others want as much automation as you can get.

In our cover story, Abby Monaco of Intercept Technology discusses the changing landscape of PCB design tools, and lays out some of the steps Intercept has taken to provide more automation and greater control, along with the attendant trade-offs.

In an interview, UTC's Stephen V. Chavez, a frequent speaker at the Design Forum, explains why he prefers a combination of control and automation, and why mastery of your tool is paramount. Guest Editor Kelly Dack discusses, in an interview, why he prefers manual control for tasks such as autorouting, and why such preferences are usually based on a performance problem found in full automatic mode. And columnist Barry Olney explains why Dale Parker's push for AI in EDA tools is dead-on, starting with automating many of the repetitious tasks involved in every design.

What do you think about the idea of having artificial intelligence built into your EDA tools? Let me know what you think! **PCBDESIGN**

**Andy Shaughnessy** is managing editor of *The PCB Design Magazine*. He has been covering PCB design for 16 years. He can be reached by clicking here.

-

#### by Abby Monaco INTERCEPT TECHNOLOGY

We are the automation nation. We are the high-speed demons, the low-frequency artists, the mixed-signal designers that make up the electronic design automation industry. We spend most of our working lives behind software, delivered to our fingertips with the promise of making things easier, faster, better, and getting us to our deadlines ever faster.

As a dedicated software product manager and a hands-on marketing director, I've seen trends in the efforts of software vendors to deliver automated portions of the design cycle. Some areas have been a great success, some areas have been a partial success, and some have just flopped all together.

There is an increase, year-over-year, in resources spent on the software vendors' side to help end-users reach success on a per project basis. There is a greater cry for freedom from designers who feel hampered by their very constrained, overly populated boards. Automation is a big part of the picture in these cases, and the growing complexity of PCB designs begs the question of where we begin to see diminishing returns on these efforts to make design "simpler" to accomplish. So often, a software tool promises a miraculous boost in productivity, only to leave users spending the same or more time correcting the automated processes that simply can't complete an area of design that needs fine tuning from an experienced hand.

# Trends in the Beginning Phases of Design

#### The Automatic Stackup Builder

As PCB design software has matured, more and more of the processes outside the actual design have become incorporated into the design cycle. One such error-prone area is the PCB designs and the actual substrate onto which they will be manufactured. Basic CAD systems tend to only define the number of routing layers, which

# Solve Challenges & Add Value with Traceability

### How does an effective traceability system impact manufacturing?

Find out with Brady's Traceability Whitepaper. This report explains:

- Cost, process and product quality improvements

- Why traceability is critical

- 4 key benefits of traceability

- Considerations for implementing a system

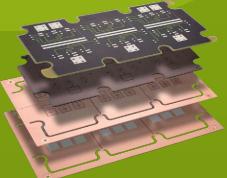

Visit BradyID.com/trackingPCB to download the Traceability Whitepaper. is a gross simplification. A typical FR-4 board is layer upon layer of core and prepreg materials that have specific heights and requirements. Even the typical copper route has a height that should be taken into account. As designs are becoming denser and more complex, greater attention is given to how to design a stackup with the best materials and configuration that satisfy both cost and the design requirements.

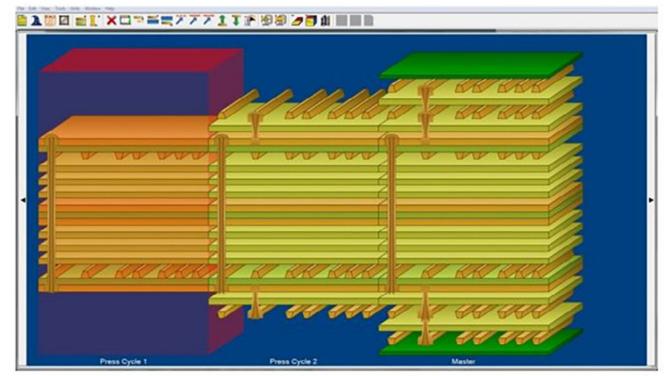

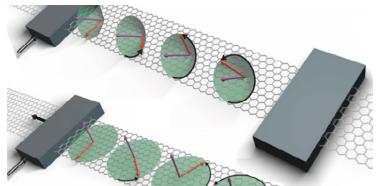

To aid designers and engineers in this area of greater attention, there is a movement toward pre-layout, software driven, stackup builders which help predict the board characteristics more accurately, and with greater signal integrity, which reduces the need for as many design changes throughout the layout process. Engineers and designers can more closely examine a board stackup, with visual cues for dielectric (prepreg) layers in between metal layers, blind and buried vias, as well as trace widths and heights within the stack. They can also attempt to prevent unexpected manufacturing flaws because many of these stackup builders include the manufacturer's specs or allow companies to build their own proven specs into the system for reliable re-use.

Since there are a vast number of manufacturers, and so many of them tend to have their own specs, Intercept chose many years ago to upgrade its stackup options to take height, dielectrics, and materials into account for easier output and drawing creation. But a more widely recognized expert in this area is Polar Instruments Inc., which has created its Speedstack tool set to allow quick and accurate stackups to be built and analyzed prior to the actual layout phase of the design cycle. They have even begun offering materials libraries that are either a generic set of information for easy building, or an actual list of materials as specified directly from some manufacturers. (Note: Materials libraries are offered as a service to customers. but are not guaranteed to be fully up to date at any given time.)

#### **The Constraint Browser**

Nearly every mid-to-high-end software vendor now offers full design constraint capabilities, from building simple design rules all the way to complex, formula-driven high-speed constraints. This is an area of automation that has allowed a boom in the high-density board

Figure 1: A view of a stackup built in Polar Instruments' Speedstack HDI software.

| Board/Block/Design                 | Units |          | Filter List            |       |             |            |               |               |           |             |             |           |    |

|------------------------------------|-------|----------|------------------------|-------|-------------|------------|---------------|---------------|-----------|-------------|-------------|-----------|----|

| <internal>:board •</internal>      | in    | ٠        | Net Name               | Group | Match Class | Match Tol. | Actual Length | Target Length | Tolerance | Min. Length | Max. Length | Max. Vias |    |

| A Technology Rules                 |       |          | M2.A/7)                |       |             |            | 0.7823274     |               |           |             |             | 110000000 | 1  |

| - Define Rules                     |       | M2 4/8   |                        |       |             | 0.9205162  |               |               | •         |             |             |           |    |

| - 🗊 Stackup                        |       | - 1      | N2 A/9                 |       |             |            | 1.1621854     |               | *         |             |             |           | 1  |

| - <b>2</b> Va                      |       |          | M2 A/303               |       |             |            | 0.59245       | •             |           | •           |             |           | 1  |

| - Component                        |       |          | M2 A/ID                |       |             |            | 1.0705992     |               |           |             |             |           | ll |

| -CIE Component Class-Class         |       | M2.A/2.8 |                        |       |             | 0.8726854  |               | *             |           |             |             |           |    |

| Clearance Rules                    |       |          | M2 A/23                |       |             |            | 1 1.243835    | 2.42          | 0         | 2.42        | 2.42        |           |    |

| 🕀 🖉 Net Rule Set                   |       |          | M2 A(34)               | -     |             |            | 0.81282.54    |               |           |             |             |           |    |

| 문 관 Net Rules<br>문 Net Class-Class |       |          | MZ BAD                 | -     |             |            | 0.9549254     | 2.416         | 0         | 2.416       | 2.416       |           |    |

| Fill Rules                         | Rules | - 1      | M2 BA1                 |       |             |            |               | 2.413         | 0         | 2.413       | 2.413       |           |    |

| Area Rule Sets                     |       |          | M2 642                 | -     |             |            |               | 2.55          | 0         | 2.55        | 2.55        |           |    |

| Diff-Pair Rules                    |       |          | M2 CASN                |       |             |            |               | 2.391         | 0         | 2.301       | 2.301       |           |    |

| Assign Rules                       |       | - 1      | M2 CKE 0               |       |             |            | 0.9862624     | 2.462         | 0         | 2.462       | 2.462       |           |    |

| Component                          |       |          | M2 CLIQN               |       |             |            | 1.909514      |               |           |             | 8           |           |    |

| - J" Nat                           |       | - 1      | 142 (112               | -     |             |            | 1.1543386     |               |           |             |             |           |    |

| Diff-Pair                          |       | - 1      | M2 CLK                 | -     |             |            | 1.3536437     |               |           |             |             |           |    |

| . I High Speed Constraints         |       | - 1      | M2 CLION               | -     |             |            | 1.3747794     |               |           |             |             |           |    |

| - / Define Rules                   |       |          | M2 CSNO                | -     |             |            | 1.1612031     | 2.427         | 0         | 2.427       | 2.427       |           |    |

| - TF Parallelism                   |       |          | M2 00/0                |       |             |            | 0.7442764     |               |           | *           |             |           |    |

| -7% Signal Path Class              | 8     |          | MZ DQ(1)               |       |             |            | 0.7879971     |               |           |             |             |           |    |

| 🚊 💰 Assign Rules                   |       |          | M2.00(2)               |       |             |            | 0.039863      |               |           |             |             |           |    |

| - From-To                          |       |          | M2 DQ(2)               | -     |             |            | 0.8079489     |               |           |             |             |           |    |

| - Parallelism                      |       |          | M2 DQ/0                |       |             |            | 0.9738197     |               |           |             |             |           |    |

| - 🎊 Signal Path                    |       | - 1      | Lun no.n               |       |             |            | A             |               |           |             |             |           |    |

| - XX High Speed                    |       |          | M0_DQ(26) -<br>M2_A(6) |       |             |            | <b>ee e</b> 4 | 1 2 20        | -         |             |             | MB_DQ(    |    |

Figure 2: Intercept's constraint browser.

design area, has made autorouting ever more powerful, and has eased the headaches of high speed design requirements.

But this area of automation is a nightmare for some, while others sometimes find that the functions they really need simply aren't available. Some EDA software programs aimed themselves squarely at the electrical engineers with more of a chip design mindset, which ended in programs offering a confusing maze of endless possibilities, to the point that no one could achieve any productivity gains. Some call this the familiar "giving them the whole kitchen sink" approach, which software programmers familiar with the importance of the user experience would call an epic fail. It doesn't matter how brilliant your engineer is, the days of keeping a manual beside your digitizer and cards sitting over your function key options are over.

Intercept's approach to this movement was to build a constraint browser that offers a high level of functionality, just under the surface of a much simpler-to-use set of options. Constraining a board has to be done in a systematic, simple fashion, or it will become over constrained, unroutable, and time-consuming to complete. With Intercept's constraint browser in its Mozaix schematic and Pantheon layout software, users are presented with sets of options that layer upon one another. Simple net clearance rules are set up first, and then area rules can be defined where specific areas of the board don't fit the main clearance rules. This can be made more intricate if needed by adding class-to-class rules, or via or component rules. For designs with diff pairs, there are options to define diff pair rules and net constraints.

Finally, there is a full section in Intercept's constraint browser dedicated to just high speed constraints. This is the area where there seemed to be a desperate need to simplify what designers and engineers are trying to accomplish. To make it easier for users, the Intercept constraint browser presents itself very simply as a way to select net names and constrain them to specific minimum and maximum lengths. This seems to be what most high speed designers are happy to use as-is. But behind this surface are many

more options, such as adding equations into cells instead of hard values, or even creating signal paths to chain a full set of nets together from the beginning of the signal all the way to the end. The levels of complication can become great, but with Intercept's interactive checking throughout the browser, users are steered away from creating impossible configurations.

It is imperative to note here that while the automation of design constraints is now readily available in most EDA software, it still remains incumbent on the users to understand what they are doing. While some software vendors might present things in easier or harder to accomplish ways, it is still ultimately the engineer or designer who will help or hurt the design process.

# Trends in the Middle Phases of Design

#### **Auto-Placement**

The concept of laying out the components on a board automatically is not new, but it is a constant area of development. Placing components by functional region, placing them per defined groups, or using assisted placement from the schematic has been around in some form or fashion. It is fair to say that most vendors offer some or all of these features to make plac-

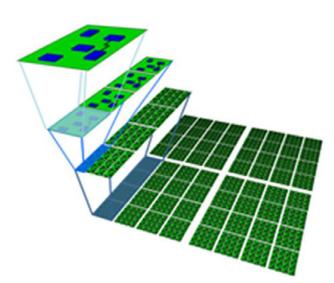

Figure 3: Example of design reuse as applied to a panel array design.

ing components faster and easier, and that they tend to do the job of saving time well enough.

But beyond single component placement, EDA software vendors have moved into the area of blocks of functional components and their circuitry. These circuits are placed in a library for reuse and revision tracking, and are pulled into a layout for placement any number of times. Many vendors handle the reuse of blocks of circuits through a glorified copy-and-paste mechanism, which often presents problems because the copies are not traced back to their original, or they are not checked as part of the whole physical board.

Intercept's strategy was to develop a fully intelligent and reusable block of circuitry in Pantheon, called a "block geometry." Areas of circuitry that are used over and over again with little modification can be defined as block geometries and placed into the layout as a block array in a matter of seconds, and modified where needed without losing its links back to its parent block geometry. This allows major revisions of the block to be updated across the entire layout, with individual modifications (such as moving a component to avoid a drill hole) preserved. Repetitive circuits can even be defined as blocks within blocks, thus allowing design changes to be done in a matter of minutes. This technology has been used by Intercept's customers to place entire block panel arrays in minutes, whereas in the past it might have taken days.

#### Autorouting

Autorouting has been around for a very long time. But the trends surrounding it are changing. The simplest autorouters use a mixture of net class spacing and width constraints along with a layer's specified autoroute directions (horizontal/vertical, axial/diagonal, etc.), and attempt to generate successful pin-to-pin routes. These autorouters tend to create some nasty routes that are nowhere close to the desired result. But it is generally accepted that while these routers require further work to fix some of the anomalies that occur along the way, they are still saving time in the end.

But for the growing number of high density boards, or boards with diff pairs and high speed tuning, there is a movement toward throwing

The ANS team is devoted to technological innovation as well as providing our customers with a high rate of satisfaction and speedy service. With our strengths in R&D, we produce PCBs that meet your specific requirements promptly, and at competitive prices.

The ANS mission is to pursue product and service excellence through continuous improvement in a quest for Total Customer Satisfaction.

Head office: ANS Industrial Co. Ltd. Kowloon, Hong Kong Tel: (852) 2757 1882

### www.anspcb.hk

### REQUEST A QUOTE TODAY!

### Factory:

Remapp PCB (Foshan) Co.,Ltd. Guangdong Province, China Tel: (86) 757-8862 3888

### Email: sales@anspcb.hk

### **PRODUCTS**

Blind/Buried/Stack via technology

Heavy copper /Pressfit Technology

Multi-layered aluminum board lead-free HAL

8 layer rigid-flex 30mm flexible finished thickness

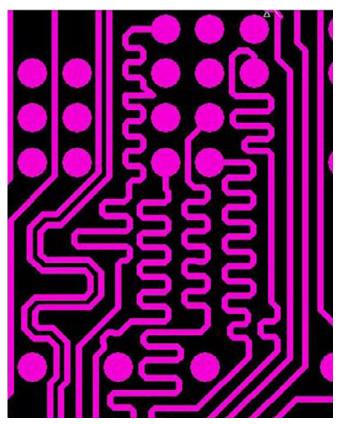

Figure 4: As higher densities, tuning and diff pairs become more prevalent in mainstream PCB designs, autorouters are struggling to keep up with more complex anomalies. It becomes a question of whether such anomalies are worth trying to algorithmically improve, or whether hand routing is returning to the picture.

out the autorouter all together. Designers have begun realizing that spending all their time trying to get a good outcome in a complex autorouting environment is an equivalent or even longer phase of the design cycle than if they simply hand routed sections of their board.

The reason for this is because autorouters require certain setup for a good outcome. Mainstream designs are becoming full of BGA breakouts, diff-pairs and nets tuned in all axes (not just X and Y, but through the Z as well!), and areas where all these complexities neck down and tune under completely different rules. But teaching the autorouter all of this can sometimes take so long that the user might as well have used manual routing to accomplish what in many cases is a better outcome than anything a routing algorithm could produce.

To better fill in for the gaps in the full autorouters, EDA vendors are now offering some very nice semi-automatic routing options such as routing all wires of a bus line together, routing and tuning diff-pairs one at a time, or region at a time, and handling breakouts from dense pin arrangements in various systematic ways. The very basics of the process are also improving with better visualization such as realtime, guided routing and quick via placement without the need for so many mouse clicks. All of these options are continually honed and improved, providing greater flexibility in response to designers' increasing level of difficulty.

While EDA software has run the gauntlet between fully manual, to fully automatic, to everything in between, it's fair to say that auto-routing will remain an ever-evolving area of the design cycle. The vendors all provide tools to help users get their jobs done, with different strengths and weaknesses, but it seems that the sweet spot for this area of design is in the semiautomatic: neither manual, nor fully automatic.

#### **Auto-Tuning**

High-speed design and auto-tuning are an area of complexity that are continually running into roadblocks. There is no advisable fully automated solution to this area of design. Try auto-tuning 24 wires all at once, and you have nowin collisions. Try just a few wires at a time, and your remaining wires can't find enough space to trombone their way together. Back and forth you go, until you delete all the wires and start manually tying up wire after wire, using every mil of space you can to save space for the next tune.

But here is the ingenuity of it: as you are stuck routing your wire and tuning as you want it tuned, automation is right at your fingertips.

Figure 5: Programming a full autorouter to break out a diff pair bus line and tune the pairs accurately could take hours. Using newer bus line routing options and auto-tuning per diff pair to allow for close checking of the outcome has become much preferred among designers.

# **SILVER Lining...** Priced with the market COOLSPAN® TECA thermally & electrically conductive adhesive

COOLSPAN® TECA Film provides an easy solution to solving your thermal management challenges. Available directly from Rogers Corporation, without the middleman, COOLSPAN TECA is supported by Rogers' technical staff to help you gain the best result from this environmentally stable conductive adhesive. Keep your cool and maintain your budget.

- · Epoxy-based Adhesive Film

- · Market Priced to Silver Spot Price

- Excellent Thermal & Electrical Properties

- · Predictable Flow

- · Durable & Reliable

Contact Rogers Corporation for more information or to request a sample USA - AZ, tel. +1 480-961-1382 • EUROPE - BELGIUM, tel. +32 9 235 3611

**SILVER MARKET PRICE**

CORPORATION

Advanced Connectivity Solutions www.rogerscorp.com/COOLSPAN

Figure 6: Tuning in tight areas can be a nightmare, whether automatic or manual.

With Intercept's Pantheon, the wire displays in red if you make it too long, blue if make it too short, and the target length is continually reported at the cursor tip so you know how you are doing along the way. Here we are, again concluding that sometimes only the semiautomatic method can be the real winner in the end.

# Trends in the Completion and Post-Processing Phases of Design

### **Bill of Materials Creation**

It seems that no matter how many flexible options software vendors offer, bill of materials creation remains a largely customized, scripted affair across a large portion of the industry. Every manufacturer has different BOM requirements and formatting expectations, and every EDA customer uses slightly different methods to specify the same information as everyone else. The result is that no matter how flexible the EDA software vendor tries to make the process of BOM creation, it seems to fall short in one way or another.

Intercept attempted to address these issues in both its Mozaix schematic and Pantheon layout applications by collecting information from every customer with a custom BOM output process and collating each requirement into common needs and special needs per customer. Common needs were addressed first, such as column width definitions, which property values to output, adding custom company headers, template setup, and real-time preview of the BOM output to aid the setup process. Then, to address the various needs of customers beyond the basics, two separate generic report tabs allow for customized reports to be appended to the BOM report, or output as separate files.

But on and above these efforts, it seems that greater unification of file formats among manufacturers is needed to really smooth this process into something that can be automated. With so many manufacturers across the country, this is probably not a likely change in the near future, and this output will probably continue to lack an easy path toward automation.

### FAB & Assembly Drawings

It is fair to say that many EDA vendors have earned a bad reputation in the area of fabrication and assembly drawing output capability. For all the sophistication offered to accomplish the PCB layout, it is often a nightmare getting the finished layout submitted for fabrication. Some vendors use DXF outputs to AutoCAD or third party processing applications to aid the assembly and fab drawing process, which is an embarrassing admission of failure for the EDA software vendors. This is also a breakdown in the design cycle and can introduce errors between the finished board and the actual drawings that get sent for fabrication.

One such company that has helped the industry quite a bit in this area is Downstream Technologies. Their flagship product, BluePrint PCB, offers easy to use software to aid designers with the final post-processing phase of the design cycle. They have done a very nice job of addressing areas where EDA vendors have fallen short.

But not all vendors are completely without drawing capabilities. For the applications that

# Superior Quality Begins Here.

Since we first began in 1985, delivering the highest quality products possible has been our first priority. Our quality control systems are certified and we renew our commitment to quality each and every day.

Delivering quality products on time, combined with timely and accurate communication from our customer service team is how we create lasting relationships with our customers.

### Take a look at our quality »

### **COMMERCIAL • MILITARY • MEDICAL • BAREBOARD**

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

Figure 7: BluePrint-PCB helps designers produce comprehensive electronic drawings to drive PCB fabrication, assembly and inspection processes.

try a little harder, the job can be more manageable but is still time consuming. For example, many require designers to continually edit and output the same drawing time and again because there is no way to view the board more than one way on a drawing. This means that the finished drawing document may or may not be able to be produced again when back in the layout software.

This is an area where Intercept has remained fairly strong. Drawing creation and output remains static so that the information trail from layout, to drawings, to output format can be followed systematically. The same board can be viewed from the top or bottom on the same drawing page, with different layer sets per view. If the board changes, a simple update can be triggered so that new drawings can be output.

## How the EDA Design Automation Nation is Evolving Today

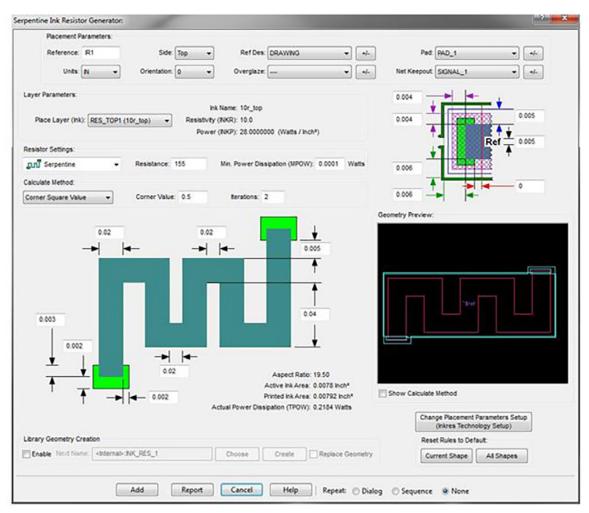

All in all, automating PCB design is moving in the right direction. The days of ground breaking new PCB software options are slowing slightly with the maturation of the market, allowing for more robust options to be incorporated into the existing infrastructure of the EDA software environments. For Intercept, this has allowed further exploration into their specialty design options for hybrid and RF design. Pantheon and Mozaix were recently enhanced to offer brand new, up-to-date ink resistor generation, answering a need for very precise and accurate ink configurations on hybrid and RF boards.

Intercept is also keeping a close focus on devices and operating systems, such as the proliferation of Apple laptops in EDA workplaces. Making software available on any operating system and through whatever device users want to use will be important going forward, and may even change the dynamic of how software is developed overall. The management of raw code across many different operating systems is not trivial.

The movement of the PCB layout world toward MCAD systems is continuing forward at a decent pace as well, with 3D modeling systems working more closely with MCAD to model boards and identify problems quickly in the de-

# SCGA-500 GF220, GF265, GF300 High-performance materials for high-frequency applications

| Key product features:                           | GF220 | GF265 | GF300 |

|-------------------------------------------------|-------|-------|-------|

| Consistent permittivity in high frequency range |       |       |       |

| Low Df at high frequency                        |       |       |       |

| Excellent thermal resistance                    |       |       |       |

| Low moisture absorption                         |       |       |       |

| Stable properties in high frequency range       |       |       |       |

Learn more about SCGA-500 Series Materials

www.paramount-usa.com

Figure 8: As ink resistor technology continues to become more prevalent in PCB designs, Intercept answers the need in its Pantheon layout application with its brand new, up to date Ink Resistor Generator.

sign phase. But sometimes the added productivity of this movement can be questionable, since STEP model support and setup is not always as automatic as it is said to be. Since the MCAD department will still require its own analysis and approval, and still uses its own native systems, it remains to be seen how the marriage of PCB to MCAD will play out.

As for the approach EDA software vendors are taking to these topics and so many others that encompass our world of automation, the most successful is through the tabulation of information gleaned directly from the users. At Intercept, we keep close tabs on the pulse of information, from social channels all the way down to support channels. Areas of frustration are important to listen to, but there is magic in the resounding silence received when an enhancement is a success among users. EDA vendors must have open eyes and ears at all times. **PCBDESIGN**

Speedstack HDI and BluePrint PCB images were used with permission of both companies, respectively.

**Abby Monaco,** CID, is with Intercept Technology Inc. and has 15 years of experience in EDA. This article was written in collaboration with Downstream Technologies and Polar Instruments Inc.

-

# BEST-IN-CLASS PRINTED CIRCUIT BOARDS FOR POWER ELECTRONICS

### **1. SOLUTIONS FOR HIGH CURRENTS**

Heavy Copper Boarde.g. for AC/DC and DC/DC converter

Inlay Boarde.g. for start-stop systems

### **2. SOLUTIONS FOR HEAT DISSIPATION**

IMS Boarde.g. for LED headlights

#### **Cool Board**

e.g. for cell connectors and battery switches

### 3. SOLUTIONS FOR HIGH CURRENTS AND LOGIC ON JUST ONE PCB

Power Combi Boarde.g. for electrical pumps

PROJECT HI-LEVEL

### Smart p<sup>2</sup> Pack<sup>®</sup> (Power Embedding)

- e.g. for electrical motors

- Iow-inductance solutions

- improved electrical, thermal and EMC features

- miniaturisation due to new interconnect approach

Schweizer Electronic AG Einsteinstrasse 10 78713 Schramberg, Germany T +49 7422 512 0 info@schweizer.ag

www.morethanPCBs.com

# The Case for Artificial Intelligence in EDA Tools

### by Barry Olney

IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

I-Connect007 Editor Andy Shaughnessy reported that the keynote speaker at the IPC APEX EXPO Design Forum was Dale Parker, a former PCB designer at Shure who is now a CAD manager at Google X. Parker is involved in the development of autonomous vehicles and all sorts of other great ideas at Google X. According to Andy, Parker told the crowd, among other things, that EDA tool vendors need to trash all their old 1990s code and start over, this time with artificial intelligence.

There has been a lot of activity in the field of AI recently, with such developments as voice recognition, unmanned autonomous vehicles and data mining to list a few. But how could AI possibly influence the PCB design process? This month, I will take a look at the endless possibilities.

So much time is wasted on reproducing the same thing over and over again on each layout. Current EDA tools, with all their bells and whis-

Figure 1: Artificial intelligence is part of the future of EDA tools.

tles, are still very limited in automation processes and mostly rely on the skills and foresight of the engineer and PCB designer to drive the software through all the hoops. Instead, EDA tools need to predict what the designer is trying to do, then look at previous designs to suggest alternatives and auto-complete the design where possible. AI is a system that perceives its environment and takes actions to maximize its chances of success.

Automating many of the tedious steps in setting up the initial database would be a good start. A standard form factor could be used to establish the initial layout environment ensuring that designs are compatible across multiple generations of technology. Although some PCB layout tools allow the designer to load a standard set of predefined startup configuration files, there is still too much manual intervention required. The PCB database could predict the fundamental design rules and via stack re-

quirements sourced from previous experience.

Predictive text, which we all use every day on our cell phones, could provide self-evident naming conventions for supplier part numbers and database fields, greatly speeding up the design definition. Busses and interfaces could be analyzed and categorized with naming conventions interpreted from the chip pin name assignments, eliminating much of the monotonous schematic capture process. IC power pins could have powers supplies assigned based on datasheet requirements. And a starter set of decoupling capacitors, added to each power pin, could kick off the PDN analysis

# POWERED BY SCIENCE...

and Industry's

**Best Technical**

Team

UYEMURA

**USA**

Uyemura PCB finishes are best in class...

... but our greatest strength is our technical team. UIC field and development specialists have an average of 26 years in the PCB industry, and a wealth of knowledge about how to make your shop succeed on all levels.

### ENIG

Al Gruenwald

George Milad

David Rund

John Meyers

Jon Bengston

The industry standard for producing uniform mid-phos EN deposits with a thin topcoat of immersion gold, over copper. Solderable and aluminum wire bondable; no dummy plating.

#### ENEPIG

Only UIC has multiple options - alloyed and non-alloyed palladium baths - so you can choose for highest stability, greatest speed, substantially improved diffusion layer for optimized corrosion protection, widest processing window.

### Via Fill Coppers

Including EVF-N, which simultaneously plates through-holes and blind vias (even those smaller than 150 µm), reducing process time by 50%.

### www.uyemura.com

Robert Coleman

**Rich DePoto**

Mark Eonta

Pat Valentine

Don Gudeczauskas

based on previous capacitor availability and parameter selections.

A selection of predefined library components could be offered, based on an initial bill of materials, and pre-placed on the schematic predicting the designer's requirements. IBIS models could be automatically assigned to each chip, based on the part number and all the interconnecting transmission lines identified. The IBIS model's source and load impedances could be extracted to assign the required impedance and terminations to each individual transmission line.

Also from this, the board stackup could be created based on previous designs, with similar technology, selecting dielectric materials, from a well maintained library, sourced from the preferred fabricator availability, dielectric loss and bandwidth requirements. Data and address busses together with clock/strobe different pairs, defined at the schematic entry level, could be assigned to certain layers in order to minimize crosstalk, electromagnetic emissions and return path loops. Power plane shapes could be automatically defined based on component placement and on the pins that need to be connected, allowing for DC drop and maximum current supply. to anticipate which blocks might be useful in future designs and these could then be made available to other designers on the corporate intranet. A database of reusable placement and routing blocks could be made available so that the intelligent database can readily identify a suitable block to drop into the design-the selected block could then be automatically adjusted to the specific needs of each instantiation.

Intelligent forward and back annotation would be a definite godsend. Traditionally, the schematic capture and PCB layout software were developed as separate applications coupled by the annotation process. Why can't we have a common database for both schematic and PCB totally eliminating the constant need to update in one direction or the other? When an ECO is implemented on the PCB, the schematic should instantly know and understand the changes and vice-versa. Over the years, forward and back annotation has been one of the most frustrating and time-consuming issues.

The intelligent database could suggest placement of critical components based on the established design rules, matched delays of busses and define routing strategies based on the technology used. But, will autonomous routing ease PCB gridlock? Placement changes could be

Memory blocks whether they be synchronous, asynchronous, source synchronous, clock-forwarding or embedded clockcould be recognized and standard design rules deployed. Busses and interfaces could be also analyzed and recognized. The entire design rule set could be built from a combination of these requirements and those learnt from previous similar designs.

Functional blocks that the designer is working on, could be scrutinized in order

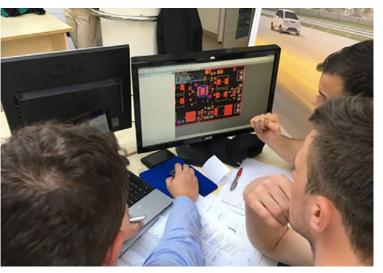

Figure 2: SMT assembly production line (Courtesy Juki).

made to open routing channels and land sizes adjusted automatically to ease routing based on design rules. The AI router could decide which layer and direction to route a bus in order to alleviate bottlenecks that generally occur in the center of the board.

The PCB project deliverables such as Gerber, IPC-2581B or ODB++ and pick-and-place files could be automatically generated based on the established design constraints. Fabrication documentation could also be auto-completed based on established standards.

On the assembly side, Internet of Things (IoT) manufacturing is currently being deployed. This system supports live bidirectional data flow between all electronics manufacturing shop floor machines and processes creating a "smart" factory with "plug and play" deployment. This allows an organization to overcome the bottleneck of establishing efficient machine-to-machine and machine-to-human communications.

I'm sure both you and I could come up with many more ideas to intelligently automate the PCB design process if time permitted. And although such a tool is many years off, the concept behind the EDA AI tool looks promising. PCB designers can certainly use all the help they can get. And, having the design tool intelligently automate their work flow could substantially speed time-to-market.

However, there is already considerable resistance to AI with some suggesting it many create too many erroneous results to be useful, and cannot be trusted. There is also the potential downside that AI might work too well and reduce the skill level needed for the role of the designer to simply indicating the goal and examining the results—but that is a long way off!

#### **Points to Remember:**

• Dale Parker, CAD manager with Google X, said in his Design Forum keynote that EDA tool vendors need to trash all their old 1990s code and start over, this time with artificial intelligence.

• Current EDA tools, with all their bells and whistles, are still very limited in automation processes and mostly rely on the skills and fore-sight of the engineer and PCB designer.

• Automating many of the tedious steps in setting up the initial database would be a good start.

• Predictive text could provide self-evident naming conventions for supplier part numbers and database fields greatly speeding-up the design definition.

• A selection of predefined library components could be offered, based on an initial bill of materials, and pre-placed on the schematic predicting the designer's requirements.

• The IBIS model's source and load impedances could be extracted to assign the required impedance and terminations to each individual transmission line.

• The board stackup could be created based on previous designs with similar technology.

• Functional blocks that the designer is working on, could be scrutinized in order to anticipate which blocks might be useful in future designs.

• Intelligent forward and back annotation would be a definite godsend.

• Placement changes could be made to open routing channels and land sizes adjusted to ease routing based on design rules.

• The project deliverables such as Gerber, IPC-2581B or ODB++ and pick and place files could be automatically generated based on the established design constraints.

• IoT manufacturing is currently being deployed creating a "smart" factory with plug and play. **PCBDESIGN**

#### References

1. Richard Quinnell, AI for software development, <u>www.edn.com</u>.

2. Mentor, Valor software documentation, <u>www.mentor.com</u>.

3. The ICD Stackup and PDN Planner software can be downloaded from <u>www.icd.com.au</u>.

**Barry Olney** is managing director of In-Circuit Design Pty Ltd (ICD), Australia. This PCB design service bureau specializes in board-level simulation, and has developed the ICD Stackup Planner and ICD PDN Planner software. To read past col-

umns, or to contact Olney, <u>click here</u>.

# **Design Automation Tools, Today and in the Future**

### by Andy Shaughnessy

Kelly Dack has been designing PCBs for over three decades, at OEMs of all kinds. Now a PCB designer with a Washington state contract manufacturer and a certified trainer with EPTAC, Kelly enjoys waxing philosophic about PCB design and design automation in general. I asked Kelly to answer a few questions about the direction EDA tools are headed, and whether he'd like to see more control, or more automation in his PCB design tools.

#### **Andy Shaughnessy:** You've been a PCB designer for quite a few presidential administrations, shall we say! In general, what do you think of today's design automation tools?

**Kelly Dack:** I've heard them described by different designers as just different sets of hammers, in that they all get the jobs done. That classic metaphor might need to be modified a bit. Take for instance a modern roofing hammer. With the help of a nail gun, utilizing pneumatics and standard-

ized nails on reels, hammering a shingle onto a roof is now highly automated. The tool systems can be very effective, but often with automation can come frustration. My sister Karin recently purchased a nail gun to re-roof her garage. The gun kept jamming so she returned it to the store and came back with a different model. It worked for a while but then it jammed too. She ended up having to try different nail types and even exchange the gun again for a different brand in order to finish her roof. Any old timer watching the job would have said, "I could've had that job done with an old fashioned hammer by now."

I think this story could be considered metaphor for PCB design automation today. Design automation requires a consistent application and vision, budget, time, trial and error and repetitive need in order to be considered an efficient PCB design solution.

**Shaughnessy:** For your day-to-day design work, would you rather see more automation in your tools, or have more manual control? Is it just a matter of having the correct mix?

# We deliver Advanced PCB Solutions!

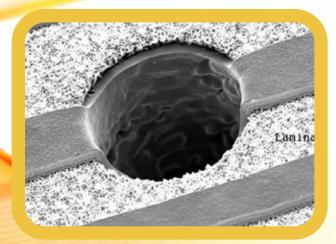

# Landless Via Technology

We're the only manufacturer in the world to have perfected a liquid photo-imageable resist (PiP) in electrolytic form, used for all our production.

CLICK TO LEARN MORE

Our unique processes enable us to create and deliver Advanced PCB Solutions that meet the needs of the demanding market at competitive prices!

# Fine line PCB, 2 mil line /space

We have developed a unique set of processes based on electro-depositable liquid photoresist.

CLICK TO LEARN MORE

# Impedance Tolerance <5%!

With our panel plating process combined with continuous foil lamination, our impedance tolerances are second to none!

CLICK TO LEARN MORE

CANDOR INDUSTRIES, INC. ADVANCED PCB SOLUTIONS

www.candorind.com | sales@candorind.com | (416) 736-6306

**Dack:** Great question and I can stick with the same metaphor. Like my sister had the vision to see her garage roof quickly finished using an automated tool, I'd love to be able to slam out board designs using more automation. But as my sister needed to pull out the compressor, order special nails, run the

Kelly Dack

hoses and replace equipment before ever starting the job, the PCB design automation strategy for a particular job may not be worth the effort. Just because we have automation tools we should not be obligated to use them unless they really improve the task at hand.

# **Shaughnessy:** In what areas of design do you usually favor more automation?

**Dack:** Repetitive processes and processes prone to human error. The CAM output routine is a simple example. The software I use allows me to set up a CAM output file routine and hit start. The two-layer, four-layer, and six-layer jobs I do usually have consistent stackups so pre-programmed routine works well. Unless it doesn't. But because my process is consistent it is easy to find where the process the error occurred. I find that output errors usually occur with something inconsistent in the design; unique patterns of associated copper that must be switched on, etc. To facilitate automation I find myself striving to be more consistent in my design methodologies.

# **Shaughnessy:** For what tasks do you prefer having more manual control?

**Dack:** Just to be clear, any preference for manual control is based on a deficiency or performance problem in automatic mode. Also, when I route. In fact, always while routing. Did I mention that I like manual control while I'm routing? Also, library part manipulation. I prefer the types of tools that allow the user to edit a part decal on a board interdependently of the library—without having to save it to the library. This allows for the odd times when the legend really needs to

stand out or one land needs to be modified to adapt to a custom processing situation.

# **Shaughnessy:** In one survey we did, about 15% of designers said their EDA tools take away too much control. Do you understand their position?

**Dack:** It would be interesting to see how those stats match up to percentage of designers laying out simple designs vs. complex designs. Working recently with a busy PCB fabricator in Seattle and a now a high-quality electronics contract manufacturer, I have seen quite a variety of designs that are very good but need minor manipulations to optimize them for manufacturing. The edits should be able to be performed in a matter of minutes. But if the layout tool requires hand-shaking with the schematic in order to move forward without "breaking," well, the layout won't move forward until the schematic is in synch. Makes sense, except when the schematic responsibility and deliverables are owned by the EE or the part decal is owned by a component librarian and are required to be fully checked and approved before being passed to the designer for use. This has the potential to slow the prototype design cycle and time-tomarket down considerably.

## **Shaughnessy:** How often do you use an autorouter? If not, why not?

**Dack:** Never! Are you surprised? This question has been asked of the design community for a long time. It is only the designers who are doing layouts with repetitive circuitry that will benefit from the time that it takes to set up the autorouter's constraints. I recall using autorouters in the late '80s and early '90s when DIP style IC memory boards were large and low speed. These were the golden years of the autorouting. The boards were consistent and very predictable. Today, I use the heck out of "dynamic" routers. Tools that allow the designer to interactively route a line or group of lines while steering the cursor in the preferred direction. Interactive modes will automatically push and shove and plow the selected lines adhering to set design rules constraints. If a problem arises, the DRC can be interactively manipulated to ease the constraint if required.

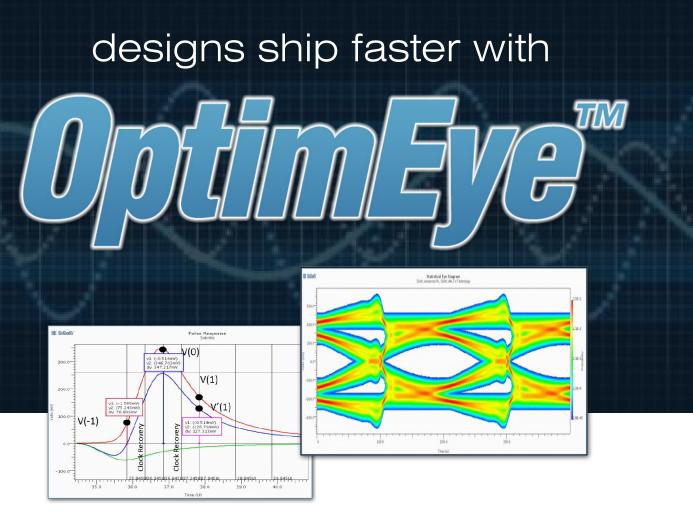

# OptimEye works with existing AMI vendor models to find the ideal balance between Tx and Rx equalization settings up to 100x faster than traditional methods.

SiSoft's new OptimEye technology lets you replace hundreds of blind sweep simulations with a single run that determines the optimal balance of Tx/Rx equalization automatically. Designed specifically for AMI-based analysis, OptimEye runs fast enough to generate custom per-channel equalization settings in a large system design with thousands of serial links.

### Learn more about OptiEye™

DOWNLOAD OUR WHITEPAPER New SI Techniques for Large System Performance Tuning Presented at DesignCon 2016

www.sisoft.com

#### **Shaughnessy:** Do you utilize your tool's design reuse capabilities?

**Dack:** Again, reusablilty is dependent on design. Many success stories of designers utilizing true reuse repetitive environments, but automatic design reuse is constrained by so many things: layer count, reference designators, etc. Reuse can require setup and agreed upon reference designators and layer counts. A lot of set rules are required between the EEs and designers or success will be limited. For simple, repetitive channels on a board, I find that using a simple "copy" routine can work very effectively.

66 Reuse can require setup and agreed upon reference designators and layer counts. A lot of set rules are required between the EEs and designers or success will be limited.

**Shaughnessy:** Do you perform post-processing and documentation manually, or use a tool such as DownStream?

**Dack:** I have great things to say about Down-Stream's BluePrint. I'd probably say great things about any other automated doc tools too, but there aren't any! DownStream has done a great job of filling this void in the EDA market. Down-Stream's BluePrint tool is a bonafide cost time/ cost saver. I can say that because while working for a Northern Nevada gaming company and pitching the idea of using BluePrint for years, a progressive manager I worked for at the time became interested and we diverted licensing fees we'd been paying for an archaic, manual form of documentation utilizing four peripheral software tools.

After installing BluePrint we reduced our entire PCB documentation time down to approximately 10 minutes! BluePrint leveraged our source database to allow us to manipulate data to specify and document a PCB in ways our source layout program could not. These guys got kudos and two thumbs up not only from me, but our entire team of designers and management as well.

# **Shaughnessy:** What current manual tasks would you like to see automated in your EDA tool in the future?

**Dack:** How about autoroute and verify based on current carrying capability? The design database has data on copper thickness and width. Let's go to the next step and be able to query current carrying capacity of a conductor! Let's be able to add current carrying constraint to a line in the schematic, route and cross-check to the constraint. Yep.

How about visual cavity creation based on height constraints? How about automated access to any spec that is called out?

How about a manufacturing constraints import? Think of it: component suppliers have provided IBIS models and are now providing step files, maybe PCB suppliers can start providing manufacturing constraints that could be imported into a design. Maybe "dynamic" quoting as the design is being laid out. Can you imagine? Say you start with a basic two-layer PCB-the supplier's sweet spot. Board starts at \$600. Then you redefine the board outline and the new price is reflected. Then you add component footprints, and vias without noticing any price change until you add that .004" diameter via. Bing! The price adjusts accordingly. Add a note for leadfree HASL, the price doesn't change. Change the note to ENIG and you see the dynamic quote indicator bump up slightly. With the influx of engineering students and even seasoned engineers performing the layout function, a tool like this would really help these newer folk to become aware of the manufacturing and cost ramifications of the design features they add.

#### Shaughnessy: Thanks for your time, Kelly.

Dack: Thank you, Andy! PCBDESIGN

# Engineering And Providing Balanced Interconnect Solutions

Miraco, Inc. • Manchester, NH • miracoinc.com • 603-665-9449 ...connecting technology

# EDA TOOLS: Automation vs. Control

#### by Andy Shaughnessy

Stephen V. Chavez, CID+, has been a seniorlevel PCB designer for almost 20 years. He is currently the lead PCB designer for the Electronic Systems Center division of UTC Aerospace Systems (UTAS).

Stephen stays pretty busy. He's the vice president of his local IPC Designers Council chapter in Phoenix, and a Designers Council Executive Board member at large, and he is recognized as a Subject Matter Expert by IPC. He often speaks at the Design Forum at IPC APEX EXPO. At this year's Design Forum, "Steph" spoke about the importance of taking charge of your PCB design education and networking.

I caught up with Stephen and asked for his thoughts on the EDA tools of today, and whether he'd prefer to have more control vs. more automation.

**Andy Shaughnessy:** You've been a designer for a few years. In general, what do you think of today's design automation tools?

**Stephen Chavez:** It's true that I've been designer for many years now and have used a variety of tool sets. In my experience, I find today's automation tools extremely useful and when the opportunity presents itself to use these type tools, they can assist greatly in the overall success of a project. Today's tools have gotten very powerful. They range from very simple to use, to very complex in nature. In my opinion as a designer, I strongly feel that when a designer progresses in his/her career and perfects his/her craft, if and when the opportunity exist, they should take advantage of these new automated tools to design a more quality product, shorten the overall design cycle, and positively affect the overall project budget. With today's designs getting more and more complex, there are instances where the only way to complete a task is to take advantages of these automation tools. Taking advantages of the horse power within these automation tools in today's design world is key and I feel these tools should be evaluated to see how they can benefit you and your employer by positively impact your effectiveness

# The standard for the Internet of Manufacturing (IoM) has arrived!

The Open Manufacturing Language (OML) is a real-time communication standard for PCBA manufacturing that defines the interconnectivity of assembly production processes and enterprise IT systems.

For the first time, IT teams, solution providers, and equipment providers can easily integrate shop-floor data to create manufacturing execution solutions based on a single, normalized, vendor-neutral communication interface.

## Take part in shaping the future!

Become a member of the OML Community where PCB Assembly industry professionals have FREE full access to the OML specification, white papers written by industry experts, and a place to share ideas in our community forum.

Visit http://www.omlcommunity.com and join the community!

as a designer and ultimately improve your company's success.

**Shaughnessy:** For your day-to-day design work, would you rather see more automation in your tools, or have more manual control? Is it just a matter of having the correct mix?

**Chavez:** For me, I'd rather have more automation in my tools. Being able to do tasks faster, work more efficiently, and producing better quality designs allows me more time to evaluate multiple options for better results and of course shortens my design cycle. With that said, having the correct mix is important too. I feel each designer has to figure out what works best for him/her and within his company. In the end, it's not the tool that makes the difference... It's the designer!

### **Shaughnessy:** In what areas of design do you usually favor more automation?

**Chavez:** For me, I'd have to say the areas of design I favor more automation are as follows: constraint input/edits/updating, autorouting, generating outputs, documentation, DFM checking (Valor), design re-use and library part creation (symbols and cells). These are areas I feel where taking advantage of today's automated tools is a must and can be a game changer.

# **Shaughnessy:** For what tasks do you prefer having more manual control?

**Chavez:** I'd prefer to have more manual control when importing mechanical data from one tool set to another that contains constraints. An

example, IDF files containing many different height restrictions and keep out zones within the PCB outline. Another area I prefer more manual control is during part placement. In this stage, not only am I placing parts on the board to optimize the routing and meeting

Stephen Chavez

mechanical requirements, I am actually routing the design mentally in parallel. This way by the time placement is 100% complete and validated with an ECAD/MCAD verification and validation analysis, routing goes rather quickly.

# **Shaughnessy:** In one survey, about 15% of designers said their EDA tools take away too much control. Do you understand their position?

**Chavez:** As I think about this question, I ask myself: "Of those 15% of designers that feel this way, what tools are they using?" Let's face it, todays tools are much better that tools of the past. Of course, the more expensive tools in the industry today—Mentor Graphics and Cadence—have more automation built in and of course more horsepower. Knowing how to use it is the trick and be willing to trust the tool. As a designer today, you should be willing to trust your tool and learn how to use it to your advantage to be more effective and successful. You can be assured that your competitor is doing this.

### **Shaughnessy:** How often do you use an autorouter? If not, why not?

**Chavez:** I prefer to use my autorouter as much as I can in every design possible. In some RF designs and in some high power designs, it doesn't make sense to use the autorouter. Early in my career, I would never use the autorouter. I just never trusted the tool that I was using at that time. As I progressed in my career and stepped into lead roles of large design teams, I learned and understood the importance of the overall design cycle. Knowing how today's automation tools can be a huge game changer regarding speed, efficiency and quality. In my opinion, it does make a difference that the tool set that I use-Mentor Graphics Expeditionhas an awesome autorouter. You just have to be willing trust the tool and learn to use it to your advantage.

## **Shaughnessy:** Do you utilize your tool's design resuse capabilities?

**Chavez:** I do utilize the design reuse but not as much as I would like. Working for a large Aero-

# PCB fabrication, assembly, and free award-winning CAD design software.

Leading the industry for over 40 years as the preferred *prototype and production PCB solutions provider* for design engineers.

#### WE ALSO OFFER:

- Best overall quality, value and competitive pricing

- Design for Manufacturability Tool: DFMplus

- Fully supported and free PCB123® design software

- Integrated assembly services

- FREE Ground Shipping

- PCBs as low as \$28 with ValueProto®

**100%** On-time Guarantee

QUOTE NOW 🔰

#### Questions? Comments? Suggestions?

We appreciate hearing from you! Contact us at: 1-800-228-8198 or via e-mail at support@sunstone.com

space company, "reuse" is important. Reuse has to be a full team effort and requires "buy-in" from the EEs to the designers to the librarians to the components engineers. It will save time in design and definitely save time down in the lab when testing out the design since the reuse portion of the design has already been validated. Taking advantage of reuse is a culture that needs to be developed and with today's automation tools, the capability is there. It just needs to be taken advantage of. When reuse is integrated into a design, reuse can be a very powerful asset to you and your company.

It will save time in design and definitely save time down in the lab when testing out the design since the reuse portion of the design has already been validated. Taking advantage of reuse is a culture that needs to be developed and with today's automation tools, the capability is there.

#### **Shaughnessy:** Do you perform post-processing and documentation manually, or use a tool such as DownStream?

**Chavez:** At the Electronic Systems Center, which is the business unit I work for within UTC Aerospace, the electrical designers (ECAD) are closely integrated with the mechanical designers (MCAD). I'd say we have a mix of automation and manual post-processing and documentation steps. We have an integrated ECAD to MCAD hand off process that has been developed and is continually optimized. This process details how ECAD generates certain outputs to MCAD which is who actual creates the final CCA drawing that is completed within a mechanical tool set. All though ECAD is capable

of creating a CCA drawing within the Mentor Graphics tool set, Mentor Graphic Expedition is an "electrical tool" for PCB design. In my opinion, it is not a mechanical drawing tool such as NX which is the tool set that our MCAD team uses. I have not had the opportunity to use the DownStream tool but I have some colleagues within the industry that have had good success with this tool and they really like it.

### **Shaughnessy:** Are there any manual tasks you'd like to see automated in your EDA tool in the future?

**Chavez:** I would like to see more options to automate manual tasks on the fly and at the designer's discretion.

# **Shaughnessy:** What would you like to see in the PCB design software tools of the future?

Chavez: In today's competitive market, first and foremost, I'd like to see the overall cost of these tool sets come down. As company's look for ways to save in expenses, it's very hard to maintain justification for using these high end tools sets when there are not being utilized to their fullest potential or if there are modules that are required to purchase within a specific toolset and may not be of much use for your actual needs. I would also like to see more of these software tools be willing to integrate better with other tool sets within their same category as well as complementing tool sets and even software such as adobe PDF and Visio for example. As I always state, it's not the tool that makes the difference but rather the designer that does. It's your career and your responsibility to progress, continue to learn, and think outside the box. It's not your employer's responsibility to train you and make you better. It's your responsibility! Where you want to end up in your career is up to you. Just know that with continued education, gaining experience and learning the use of today's automation tool sets, you have the potential to create some great magic!

#### Shaughnessy: Thanks for speaking with us, Steph.

Chavez: Thanks for the opportunity. PCBDESIGN

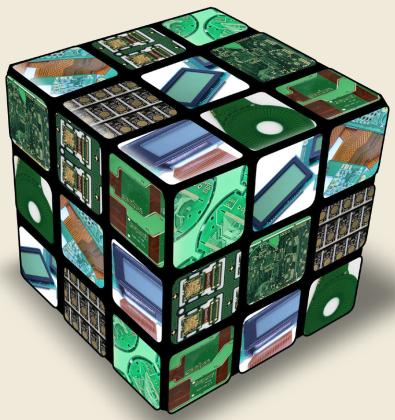

# THE SMART SOLUTION TO IMPROVE SYSTEM PERFORMANCE

# FARADFLEX ULTRA THIN MATERIALS FOR HIGHER PERFORMANCE PCBS

Faradflex is a high performance, ultra-thin laminate or resin coated copper material designed as an integral part of the PCB, module or chip package.

# FaradFlex<sup>®</sup> Improves System Performance, Price, Quality, and Reliability by:

- Reducing PCB size and/ or thickness

- Utilizing VSP Copper to provide the lowest loss signal for high speed designs

- Increasing functionality

- Improving power distribution (power integrity)

- Reducing the number of SMT Discrete Caps, Traces, Vias, Pads

- Eliminating hundreds (thousands) of SMT and etched and drilled features sites for possible failure on each PCB

For a free sample contact us at: sales@oakmitsui.com or call us at 503-313-1905

EMBEDDED CAPACITANCE

For more information, visit www.faradflex.com

#### <u>Happy's Essential Skills:</u> Failure Modes and Effects Analysis (FMEA)

Failure modes and effects analysis (FMEA) is a systematic process to evaluate failure modes and causes associated with the design and manufacturing processes of a new product. It is somewhat similar to the potential problem analysis (PPA) phase of the Kepner-Tregoe program.

# Walt Custer Elaborates on his Annual IPC APEX EXPO Forecast Presentation

IPC APEX EXPO 2016 has come and gone, and this year, Walt Custer's annual presentation forecasting the upcoming year for the industry was much anticipated, as always. I met up with Walt at the show to learn about his presentation and dig deeper into his findings.

#### IPC President John Mitchell on the Past, Present, and Future, Part 1

We conducted this interview with IPC President John Mitchell on the show floor at IPC APEX EXPO to discuss the event, the changes on the IPC board, and the key metrics that IPC uses to measure their own performance and effectiveness. John also invites the industry to a unique challenge.

#### American Standard Appoints Dave Olson Vice President of Operations

Anaya Vardya, CEO of American Standard Circuits, announced the appointment of industry veteran Dave Olson to the position of Vice President of Operations.

#### Weiner's World: March 2016

Sellers of equipment at the Shanghai CPCA event complained of continued poor business. This was especially evident amongst those selling to firms building boards for phones and other portables devices as indicated below. However, not all reports were bad. Major fabricators such as Wu's in China, not dependent upon HDI or flexible products, stated that they were "satisfied" with their current business levels.

#### Green Legislation and the Impact on Electronic Materials and Processes

In general, "green" and "environmentally friendly" refer to manufacturing that involves the replacement of toxic substances with less toxic materials, the elimination of materials or processing steps, less consumption of chemicals (i.e., more efficient or higher yield processing), reduction of water use, reduction of energy use...

#### Williams and Beaulieu: Board Shops and CMs Must Communicate Better

Two well-known consultants in the PCB industry, Dan Beaulieu and Steve Williams, have joined forces to try to help close the divide between CMs and board shops. I recently sat down with them at IPC APEX EXPO 2016 to better learn about their strategy for bringing the two sides together.

#### IPC President John Mitchell on the Past, Present, and Future, Pt. 2

In Part 2 of our on-the-show-floor interview with John Mitchell, conducted at IPC APEX EXPO 2016, John continues describing IPC's key measures, and then invites industry folks who are reading this to participate in a unique challenge—some might say experiment. The question is, will there be any takers?

#### <u>Rep. Mike Honda Visits Bay Area Circuits'</u> <u>California Facility</u>

"I am grateful to Bay Area Circuits for hosting me today," said Congressman Honda. "It's great to hear from the employees that have played a vital role in the company's success. It's a reminder of the contributions they make to this country's and California's economy."

#### The Sum of All Parts: Total Concept— Growing for the Future